As the demand for high-capacity, low-latency wireless networks explodes across residential, enterprise, and industrial environments, a Canadian innovator is quietly reshaping the way Wi-Fi works—from the silicon up. Edgewater Wireless (TSXV:YFI/OTC:KPIFF), headquartered in Ottawa, is pioneering a transformative approach to wireless connectivity with its patented Wi-Fi Spectrum Slicing™ technology and an AI-enhanced roadmap that’s drawing attention from industry heavyweights.

We sat down with Andrew Skafel, CEO of Edgewater Wireless, to discuss the company’s impressive recent milestones—including selection to Canada’s prestigious FABrIC semiconductor program, backing from Silicon Catalyst, and entry into Arm’s Flexible Access (AFA) Program. We also dove into Edgewater’s vision for AI-powered spectrum optimization and how their “standards-leading” strategy is carving out a unique path in a crowded wireless landscape.

Andrew, thanks for joining us. Edgewater Wireless has had a banner year. Let’s start with the basics—what makes Edgewater different from the rest of the Wi-Fi ecosystem?

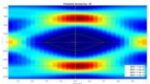

Thanks—it’s great to be here. At Edgewater, we’ve taken a fundamental departure from traditional Wi-Fi design. Instead of incrementally optimizing the existing single-channel-per-radio architecture, we pioneered Wi-Fi Spectrum Slicing, which enables multiple concurrent channels in the same frequency band—essentially “slicing” the spectrum to maximize capacity and performance.

This isn’t just theoretical. Our patented silicon architecture can deliver 10x performance gains and up to 50% lower latency—even on legacy client devices. We’re not asking the world to adopt a new standard or wait for new device rollouts. We’re enhancing performance from the infrastructure side, and we’re fully aligned with current and evolving Wi-Fi standards.

That’s impressive. Let’s talk about the AI element. You recently announced the initiation of prototyping an AI subsystem using Arm® technology. What does that mean for Wi-Fi?

It’s a big step for us—and for Wi-Fi, more broadly. We’ve entered the Arm Flexible Access Program, which gives us cost-effective access to industry-proven Arm IP. With this, we’re prototyping our next-generation Wi-Fi baseband chip using Arm Cortex® CPUs, and we’re exploring Arm Ethos™ NPUs for on-chip AI acceleration.

Why does this matter? Because we’re bringing real-time, AI-driven spectrum engineering directly to the network edge. Our patent-pending machine learning algorithms are designed to do things Wi-Fi’s never done before—mitigate congestion, manage spectrum allocation in real-time, and autonomously reconfigure channel/link density for optimal throughput—all within the chipset. This is a paradigm shift that will allow networks to self-optimize based on real-time user and device behavior.

Wi-Fi is notoriously messy in dense environments. Are you saying this AI-driven approach can solve that?

Exactly. Traditional Wi-Fi is reactive and when collisions and interference occur, it has limited ability to mitigate it, and often does so ineffectively. Our AI subsystem is proactive based on data received from the coverage area environment — delivering a significant boost to the overall QoS and transforming the user experience. Imagine your Wi-Fi recognizing a spike in video traffic and re-allocating spectrum capacity to handle the load—or rerouting traffic away from interference without any human intervention.

This is particularly crucial in environments like MDUs (multi-dwelling units), enterprise campuses, industrial IoT deployments, and even in smart homes. As device counts continue to explode, intelligent spectrum management becomes the key differentiator.

You will get unparalleled Wi-Fi QoS for all devices with Wi-Fi Spectrum Slicing.

You mentioned prototyping in Arm’s ecosystem. What advantages does that bring?

Arm has created an incredibly robust platform for innovation. Their CPUs and NPUs are energy-efficient, scalable, and deeply supported, which accelerates our time to market and de-risks development. More importantly, being part of the Arm ecosystem validates our approach and opens doors for deeper industry collaboration.

We’re not building a niche chipset—we’re creating a standards-aligned, AI-enabled platform that can be licensed by leading silicon players or deployed by OEMs, service providers, and enterprises. Working with Arm helps us do that at scale.

That leads us to another major milestone—your inclusion in the Canadian government’s FABrIC program. What does that support mean for Edgewater?

The Government of Canada’s FABrIC initiative is a game-changer. For Edgewater, it represents a national vote of confidence in our vision to lead the next wave of intelligent, AI-enabled wireless innovation. Managed by CMC Microsystems, FABrIC is a five-year $223M program to accelerate the commercialization of semiconductor-based processes and products. We’re proud to be one of the first recipients. The program provides strategic funding that allows us to de-risk R&D and accelerate commercialization of our next-gen AI-enabled Wi-Fi chipsets.

This isn’t just about money—it’s about national competitiveness. Canada has world-class talent and ideas, but turning those into commercially viable silicon solutions for the worldwide market requires deep support. FABrIC recognizes that and is helping position Canada as a global player in intelligent connectivity.

You’ve also secured support from Silicon Catalyst, the world’s only incubator focused exclusively on semiconductors. What has that partnership unlocked?

Joining Silicon Catalyst has given us access to a global network of mentors, corporate partners, and critical infrastructure for silicon development. They’ve helped hundreds of semiconductor startups navigate the journey from concept to production—and their backing speaks volumes about our technology and market potential.

The Silicon Catalyst ecosystem is already helping us refine our product-market fit, prepare for mass manufacturing, and navigate relationships with fabs and IP providers. It’s a massive accelerant for our roadmap.

Let’s step back a bit. Where do you see Edgewater Wireless headed over the next 12–24 months?

Over the next 12 to 24 months, Edgewater Wireless is laser-focused on commercializing our next-generation Wi-Fi Spectrum Slicing silicon under the PrismIQ™ product family. This family will span three high-value, global market segments—residential, enterprise, and Industrial Internet of Things (IIoT)—each with tailored variants designed to optimize performance, capacity, and reliability for dense device environments.

We’re already well through the ‘beta’ prototyping phase. Key upcoming milestones in our silicon realization roadmap include:

- Prototyping and silicon realization of our next-gen AI-enabled baseband is underway, with sampling beginning in early 2026. For those parties interested in early access to the PrismIQ product family, development platforms will be made available to select partners in the first quarter of 2026.

- Partnering with Tier-1 industry players to accelerate market deployment through licensing and joint development initiatives, ensuring broad industry alignment and faster paths to integration.

- Scaling our software stack and AI-driven algorithms to ensure seamless compatibility with evolving standards like Wi-Fi 7—and laying the groundwork for next-gen protocols including Wi-Fi 8.

- Leveraging support from strategic partners and government-backed programs, including Silicon Catalyst, Arm, CableLabs, and FABrIC, to fast-track innovation and market readiness.

Interested and qualified service providers and equipment vendors are encouraged to contact us to gain early access to the PrismIQ product family. Let’s shape the future of wireless, together.

There’s a lot of buzz around “standards-leading” versus “standards-following.” How does Edgewater view its role in the Wi-Fi standards ecosystem?

We’re deeply involved in the standards community, and we build our technology with alignment in mind. But we’re also pushing the boundaries of what those standards enable.

Spectrum Slicing is a great example—it fits within existing standards yet unlocks next-level performance by reimagining how the physical layer handles channelization and interference. That’s what we mean by “standards-leading.” We respect the standards, we align with them—but we’re also creating new categories of capability within them.

It’s not about breaking compatibility—it’s about enhancing what’s possible, without requiring changes on the client side. That’s key to enabling broad adoption.

Final question—what’s the big vision here? What does success look like for Edgewater Wireless?

Success for us means redefining Wi-Fi—not just making it faster, but smarter. Our goal is to embed AI-enabled Spectrum Slicing into the heart of Wi-Fi infrastructure and make intelligent wireless connectivity the norm, not the exception.

We believe Wi-Fi should be as dynamic as the environments it serves, and with our technology, it can be. Whether it’s in a smart home, an enterprise network, or a factory floor, we want to be the intelligence layer that ensures every device gets the performance it needs, when it needs it.

We’re not just solving for today—we’re building the wireless fabric of the future.

About Edgewater Wireless (TSXV: YFI / OTC: KPIFF)

We make Wi-Fi. Better.

Edgewater Wireless delivers unmatched Wi-Fi QoS—bar none—by intelligently mitigating congestion, managing spectrum allocation in real-time, and autonomously reconfiguring channel and link density—driving economic gains for service providers and their customers through reduced churn, improved efficiency, and high-performance connectivity in dense environments. Redefining Wi-Fi from the silicon up, Edgewater’s patented, AI-powered Spectrum Slicing platform—delivered through the PrismIQ™ product family—breaks the limits of legacy Wi-Fi by enabling multiple concurrent channels in a single band. This delivers 10x performance and up to 50% lower latency, even for legacy devices. With 26 patents and a fabless model, Edgewater is transforming the economics of Wi-Fi for service providers, OEMs, and enterprises—powering scalable, standards-aligned/leading connectivity across residential, enterprise, and Industrial IoT markets. Edgewater is building the intelligence wireless foundation for the next era of global connectivity.

Visit https://edgewaterwireless.com

Andrew Skafel is a recognized leader in wireless and next-generation Wi-Fi, driving innovation as President and CEO of Edgewater Wireless. Under his leadership, the company has pioneered Wi-Fi Spectrum Slicing, revolutionizing high-density wireless performance. With over two decades in telecom and technology, Andrew has led product development, strategy, and key industry partnerships. His customer-focused vision ensures Edgewater’s patented solutions address real-world connectivity challenges. A sought-after expert on Wi-Fi innovation, Andrew continues to shape the future of wireless communications, positioning Edgewater Wireless as a global leader in scalable, high-performance networking solutions.

Also Read:

CEO Interview with Jutta Meier of IQE