At DAC in 2011 I visited an EDA company called Silicon Frontline Technology because they offered some 3D field solver tools used to create the highest accuracy netlists that can then be simulated with a SPICE circuit simulator to predict timing, power and IR drop. A recent press release with X-FAB and Silicon Frontline looked interesting so I contacted Thomas Hartung, the VP Marketing and Joerg Doblaski, the team leader of the Design Technology Group at X-FAB to better understand their IC design process and why it required a 3D resistance extractor.

Continue reading “Why X-Fab uses 3D Resistance Extraction and Analysis”

DVCon: Hardware/software Co-design from a Software Perspective

The EDAC Emerging Companies Comittee (would that be the EDACECC?) is organizing a free panel session one evening at DVCon. It is Monday February 27th from 6pm to 8.30pm. I don’t yet have a room but it will be at the DoubleTree Hotel where DVCon is being held.

EDA companies often address hardware/software co-design from a hardware point of view as if the software somehow is going to be put together once the chip is available, and is a relatively small part of the design of the system (real men design chips). But, in fact, software is often much longer lasting than any individual chips. Much of the software in your phone may be a decade old and running on the fifth or sixth iteration of the hardware. Apple’s iOS alone ran first on a Samsung chip, and then Apple’s own A4 and A5 chips, for example. The result is that hardware and software teams look at the importance of software and software development methodology very differently.

Michel Genard of Wind River was going to moderate it, but Wind moved their sales kickoff and so I’ve been drafted in. I was VP marketing at both VaST Systems Technology and at Virtutech, both of which were heavily involved in the space (VaST is now part of Synopsys, Virtutech now part of Wind River, in turn owned by Intel).

The panellists are:

- Atul Kwatra, principal engineer, Intel Corporation (Intel own Wind River and Virtutech)

- Michael James, senior staff engineer, Lockheed-Martin Space Systems Company (Michael used to work with me at Virtutech)

- Don Williams, head of core technology, Skype (and previously headed up a software development team at Cisco)

- Bill Neifert, chief technology officer, Carbon Design Systems (a virtual platform and modeling company)

Grab a beer and come along. I hope to see you there. The panel is free. You don’t need to be registered for DVCon, nor an EDAC member.

To register for the EDAC panel, go here

To register for DVCon, go here

For more information about the panel, go here

Powering the Platforms: ARM’s 2012 Approach

A client turned me on to a great new book, “The Age of the Platform” by Phil Simon. It’s about how Amazon, Apple, Facebook, and Google have radically transformed the landscape. For me, it’s not just social networking – it’s social computing, changing how things are designed.

I’m borrowing this right from Phil’s description of why he selected these four companies as the platforms at the center of this shift:

“1) They are rooted in equally powerful technologies—and their intelligent usage. In other words, they differ from traditional platforms in that they are not predicated on physical assets, land, and natural resources.

2) They benefit tremendously from vibrant ecosystems (read: partners, developers, users, customers, and communities).”

All these platforms are making this kind of impact in large part because they run on devices powered by one company: ARM. They match the above description, as a purveyor of intellectual property with virtual design and fabrication allies. ARM processors power social computing.

ARM’s technology does one thing better right now: it puts intelligent use in a person’s hand. The ARM approach is unique in that most tasks can be done in less than 1W, and some very complex things can be done in less than 2W – which correspond to the points of interest for smartphones and tablets respectively.

A vibrant ecosystem is an understatement, and it’s building smartphone and tablet momentum. Apple’s epic success, driven by dual Cortex-A9 cores in their A5 processor, is fueling a whole new set of changes driven by BYOD and consumer trends like mHealth and the “quantified self”. Qualcomm, about to set a new bar with their Krait implementation of the ARM instruction set, has taken a lead in smartphone processing innovation. NVIDIA and Freescale have gone quad Cortex-A9, with NVIDIA rumored to have taken the socket in the next-gen Amazon Kindle Fire. TI and ST-Ericsson are on dual Cortex-A15, with first silicon just seeing the light of day. Microsoft, having swung the Windows 8 machine in the direction of ARM, is part of the equation – and we’re about to find out more about that February 29th at Mobile World Congress.

The upper right of ARM’s “Gods and Giants” roadmap shows new 64-bit cores, Atlas and Apollo, targeting 20nm implementations of ARMv8 with an eye on growing into the server market. Here the ecosystem isn’t as thriving yet, with names like AppliedMicro and Calxeda at the front. Crossing Intel’s Sandy Bridge in that direction may prove just as difficult as Intel coming across toward the smartphone side.

Where things are thriving is the center of the roadmap, for smartphones and tablets. They tipped their highly efficient Cortex-A7 core last fall, and is now looking deeply at a “big-little” processing approach where the A7 does all but the biggest tasks, with a Cortex-A15 dozing patiently until needed for brief heavy lifting. They’ve hinted at a similar big-little approach with two new graphics cores, Skrymir and Tyr, with few details so far. It seems they are looking at smooth, dynamic shifting between cores sized for the task instead of simply tossing more cores into the mix. It’s all about the 1W.

What do you think of the state of social computing, the idea of these as the new platforms, the contrast between ARM and Intel, and what’s on the horizon from ARM?

The Old Order Changeth

It is interesting watching as changes in technology bring giants to their knees. Far and away the best book on the subject is Clayton Christensen’s The Innovator’s Dilemma. If you haven’t read it then rush out and buy it immediately. In tech, you are not educated if you haven’t.

Two things made me think about this recently. One is Kodak filing for bankruptcy. Some commentary is basically critical that Kodak were blindsided by the digital revolution. But in fact they not only pioneered early digital cameras, but also predicted almost exactly the speed of adoption by government (think spy satellite), then business, and then the consumer. The problem was that nobody knew how to make money on digital cameras which are a one-off low-margin sale. It was classic Innovator’s Dilemma stuff: everyone saw it coming and even so, nobody knew what to do about it. Curiously, FujiFilm, Kodak’s big competitor has fared better and managed to diversify into other markets. But that is always a risk strategy. Most forest product companies that try to get into electronics do not become Nokia, one of the most amazing business transformations ever. Now in turn the standalone digital camera industry is itself under threat, at least the the low end. When your cell phone has an 8 megapixel camera and is always in your pocket, why do you want another camera that is only marginally better.

Talking of cell phones, here are a couple of anecdotesabout changes in technology leadership. Apple’s iPhone business is now larger than Microsoft (in revenue). Not just Office or Xbox, but all of Microsoft, a company that recently was regarded as so powerful that it should be broken up since it would otherwise be a perpetual monopoly. But here’s an even more amazing fact. Apple is now criticized as being too dependent on iPhone, a one-product company. But if you take away Apple’s iPhone business completely, then the rest of Apple is still bigger than Microsoft and pretty well diversified.

Of course for EDA, companies that ship huge volume are not a dream but more of a nightmare. Apple designs one or two chips per year and so have comparatively modest demands for EDA tools. Of course they also buy lots of silicon from Qualcomm, Broadcom and memory suppliers in particular. But since EDA doesn’t share in volume, it shares in design starts, it benefits from less concentrated market power. Lots of competitors all designing their own chips is the EDA dream (and EDA doesn’t really care if chips go into production). As a handful of companies become more and more dominant in the end markets, shipping enormous quantities of relatively few designs, I think it will be a challenge for EDA to maintain its business models unchanged. And, as has been pointed out on this site many times, it will also have a major impact on where the chips are manufactured and from where the capital for the fabs comes.

FineSim Webinar

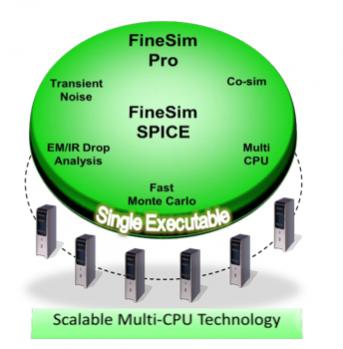

FineSim is Magma’s circuit simulator that has been doing extraordinarily well. In my opinion it is one of the big reasons that Synopsys is acquiring (presumably, still subject to approval of course) Magma. FineSim is especially strong in the memory market with over 70% of the top 5 DRAM manufacturers and the top 10 flash manufacturers using it. Plus over half of the top 20 semiconductor manufacturers. For a relatively new product this is impressive growth.

FineSim was written from the start to be scalable and to take advantage of multi-core workstations and racks of servers. This means that it scales to simulate large analog designs tha could not have been verified with previous SPICE engines. It is actually two products, FineSim Pro and FineSim SPICE.

There is a huge explosion in the need for analog, RF and mixed-signal solutions. For example, your smartphone may have as many as 10 radios in it: 4 GSM bands, GPRS, EDGE, 3 UMTS bands, HSDBA, WLAN, GPS, Bluetooth. Plus modern processes require characterization at many more than the old four-corners that we used to be able to use just a few process generations ago.

There is a new FineSim webinar that covers the use of FineSim for various kinds of simulation. It is 2-5X as fast as the competition on a single CPU and, of course, gets faster still with multiple CPUs.

Some of the things that will be covered in the webinar are:

- multi-threaded/multi-machine performance and scalability that allows you to simulate 1.7 million transistors in just 16 hours with SPICE-accurate results

- support for industry standard formats, enabling seamless integration into existing design and verification environments

- extensive reliability analysis to ensure design quality

- superfact runtime that allows you to increase test coverage with having to tradeoff against accuracy

- AMS (analog/mixed-signal) verification

- Fast Monte Carlo (FMC) flow

- FineSim RF

Register for the webinar here.

Virtuoso has got you cornered

Things you don’t know about Virtuoso: we’ve got you cornered.

That is the title on a Cadence blog item last week. It is actually about variability and how to create various corners for simulation and analysis, but given Cadence’s franchise for Virtuoso, its lock-in through SKILL-based PDKs and so forth, it is not perhaps the ideal message to be sending. There is plenty of resentment at both foundries and customers about Cadence’s lack of openness in this area.

The blog is actually about the new features in Virtuoso supporting process variation and the need in a modern design to characterize it at dozens of different points, not just in the traditional PVT (process, voltage, temperature) realm but also device parameters and even data collected from Monte Carlo analysis.

Most of the blog is about how to expand various corners without creating a combinatorial explosion where every parameter appears with every combination of others, which is not normally all that useful.

Synopsys latest acquisitions: ExpertIO (VIP) and Inventure (IP)… Any counter-attack from Cadence?

Even if ExpertIO acquisition by Synopsys, coming after nSys acquisition a couple of months ago, will not have a major impact on Synopsys’ balance sheet, it will again change the Verification IP market landscape. The acquisition of Inventure, a subsidiary of Zuken, will have a major impact on the Interface IP market, even if it’s on the Japanese market only, as Inventure was very successful on this domestic market, but only in Japan. This acquisition will also have an impact on the balance sheet of an IP vendor based in Canada, we will see why.

As already explained in a previous post, Synopsys strategy was to offer “bundled” VIP around IP sales, and this is not the best way to valorize the VIP product, as the Design IP customer expect to get a bundled VIP almost for free. After Synopsys acquisition of nSys, the acquisition of ExpertIO is likely to reflect a real strategy inflection, the company deciding to attack Cadence in the field where they were the strong leader, especially after the acquisition of Denali (May 2010), facing a competition made of small companies only (nSys, ExpertIO, PerfectVIP, Avery…).

Another side effect is now the lack of accuracy of the “Yalta description”: Cadence dominant in VIP and Synopsys in IP market! This claim is not true anymore! The VIP market is, by definition of “verification”, limited to the protocols based functions, like USB, PCIe, SATA, AMBA, MIPI, Ethernet… or to the memory interfaces like DDRn, GDDRn, Flash and so on. In other words, VIP market is far to be a huge market (even if we still don’t know the market size, as no survey has been done so far). IPNEST evaluation is between $50M to $100M, please don’t expect double digit precision! Going after this market can be a way for Synopsys to apply the “barbed wire fence strategy” as described by Ed McKernan. To protect their Interface IP market share, Synopsys is expanding their presence –extending the ranch size- to make it more difficult for the competition to attack the core business (IP)… That’s one explanation, the other could simply be that Synopsys need to expand in VIP to guarantee higher growth rate on a limited size market. You choose it!

The acquisition of Inventure is easier to understand. Anybody who has tried to develop the business on the Japanese market knows that it’s not easy; the go-to-market rules are different from the west part of the world, doing advertising is not enough, your customers expect a very high quality product (NOT a well marketed one), and an outstanding level of technical support. Needless to say, they also expect you to speak Japanese… The success of Inventure in PCI Express IP since 2007 and SuperSpeed USB more recently was certainly linked to their ability to best serve their Japanese customers. I don’t know if Synopsys was successful on the Japanese market, but I am sure that after this acquisition, they will be!

The side effect of this acquisition is that Snowbush (the Canadian IP vendor), who had built a strong partnership with Inventure by bringing their high quality PHY IP to complement the Controller IP sold by Inventure, will most probably see their PHY IP sales vanish in Japan. IPNEST evaluation was that about 25% of Snowbush revenue was made thanks to this partnership (initiated in 2008, thanks to a well known consultant – guess who). But Snowbush future will change anyway: being part of Gennum, they have been acquired by Semtech, ironically two days after Inventure’s acquisition by Synopsys!

By Eric Esteve from IPNEST

AMD and GlobalFoundries?

One thing I do as an internationally recognized semiconductor blogger is listen to the quarterly conference calls of companies that drive our industry. TSMC is always interesting, I really like the honesty and vision of Dr. Morris Chang. Cadence is good, I always want to hear what Lip-Bu Tan has to say. Oracle and Larry Ellison, Synopsys, Intel, AMD, Qualcomm, Broadcom, Altera, Nvidia, and a couple of others.

If I miss the actual call I get the transcript from Seeking Alpha. Here is the most recent AMD call Q4 2011. I post this blog as an observation and discussion rather than a report of facts and figures. I respect GlobalFoundries and hope they succeed but I do not understand the relationship between AMD and GFI. But then again, I’m just a blogger so help me out here:

Granted, the “spin-off” of a new corporate entity is a difficult endeavor, especially when AMD retained a substantial % of GFI (and ATIC, GFI’s parent company, received a substantial % of AMD).

For a while, AMD would routinely incorporate a loss in their quarterly results, based upon their percentage ownership of GF which made sense to me. Prior to the spin-off, AMD’s losses reflected 100% of the fab expense, and immediately after the spin-off, AMD’s one-third ownership of GF resulted in roughly 1/3 of the previous losses still being reported quarterly.

However, AMD’s % ownership of GFI declined, due to the increased investment by ATIC in GFI, and the acquisition of Chartered Semi. When AMD’s ownership was reduced below 15%, the declaration was that “we will no longer incorporate the ongoing financial results of our ownership in GFI in quarterly reports… the investment in GF will be treated as a long-term asset.” OK, that makes sense too.

Then, there were different classes of GFI shares issued. And, throughout 2010-11, there were repeated updates in AMD’s GAAP quarterly financials, based upon updates to the book value of the investment in GFI, in contradiction to the earlier declaration.

In a couple of cases, AMD reported a significant gain in the value of its investment, due to a recalculation of the value of its (diminished) percentage share in GF, during the acquisition of Chartered:

http://www.sec.gov/Archives/edgar/data/2488/000119312511163112/filename1.htm

However, in the most recent 4Q11 fiscal quarter, AMD recorded a loss of $209M. It is unclear to me how AMD intends to represent the ongoing value of their investment in GlobalFoundries.

Actually, it’s hard for me to believe that their value in GFI could increase, as was reported in a couple of recent quarters. AMD no longer invests in the ongoing operations of GFI, ATIC does. I highly doubt GFI is profitable, based upon the losses incurred prior to spin-off plus the integration of Chartered Semi, lacking new sources of external customer revenue. Yet, AMD has recently reported both substantial quarterly GAAP gains and losses with regards to GFI, amounts which far exceed their operating profit each quarter. This financial reporting method is very puzzling to say the least.

The “cost-plus” wafer purchase agreement that AMD established with GFI is clearly an opportunistic one for AMD, which leads to a discussion of a very unusual financial agreement:

http://semiaccurate.com/2011/04/04/amd-and-global-foundries-agreement-not-what-it-seems/

AMD is contractually bound to provide additional payments (up to $400M) to GFI this year, above and beyond the wafer purchase agreement between the two entities. The explanation for these payments was “based upon obtaining sufficient 32nm yields”. Even for a foundry blogger it is hard to understand how a wafer-purchase agreement requires an additional “bonus payment”, up to $100M quarterly. AMD must be assuming it can move lots of additional (32nm SOI) product, to make a committed payment based upon wafer yield, not wafer volume. The amount of $100M per quarter is dangerously close to AMD’s quarterly free-cash flow and non-GAAP profits.

And now IBM “quietly” starts to make chips for AMD?

So, it is not clear to me what relationship AMD and ATIC have maintained, in terms of the value of AMD’s holding in GFI, and the financial obligations (beyond customer and supplier) that AMD has to ATIC in 2012. This lack of transparency is troubling, and in my mind it brings into question the credibility of each quarterly financial report.

For that reason alone, I would consider AMD to be an unsound (long-term) investment, although it certainly makes for interesting “short-term trading”. This is an observation, opinion, for entertainment purposes only, I do not own AMD stock nor do I have investments in related companies.

There is also some good and some perplexing news from GF, unrelated to its relationship with AMD:

GFI announced that the new fab in Malta, NY, will be providing prototype wafers to IBM in mid-2012. That’s the good news.

However, it’s not really a “big win” for GFI, which may not be clear from the press release. Chartered Semi has been a second source for the processor parts used in the Microsoft Xbox 360 family. Microsoft insisted, of course, that IBM Microelectronics have a viable second source, and IBM ensured that Chartered was a qualified supplier of the corresponding SOI technology.

So, in my opinion, this current announcement is really just an extension of that second-source agreement – Microsoft clearly demanded a second source for the processor in the upcoming Xbox 720 product. However, the Xbox 360 parts were never really a large source of profit for Chartered – it was more a way for Microsoft to negotiate the best pricing from IBM. Although additional revenue for GFI is a good thing, the parameters of this agreement are likely not very different from the previous second-sourcing deal, and thus, not an exclusive, nor high-margin revenue opportunity.

The perplexing thing is that the resources invested in Malta on 32nm SOI bring-up as a second source to IBM will be diverted from 28nm bulk technology bring-up. In the 2013-2015 time frame, TSMC has made it clear that 28nm is going to be a very important source of revenue for them and I know this to be true.

Last week I sent a version of this to GFI for clarification / comment but have not heard back yet. If somebody else out there has more information or can correct me please post in the comment section or email me directly: dnenni at SemiWiki dot com.

DVCon: Formal Verification with lunch

At DVCon on Thursday March 1st (St David’s day for any Welsh readers) Jasper is sponsoring lunch from 12pm to 1.30pm. It will take place in the Cascade/Sierra ballrooms.

During lunch there will be a panel discussion Formal Verification from Users’ Perspectives with real users no how they mitigate risk in their designs while meeting the tight schedules of modern designs. The panel will share their experiences with formal verification and how the formal approach has helped them in different ways in their design and verification methodologies.

The panelists are:

- Jon Michaelson from nVidia

- Ambar Sukar from ParadigmWorks

- Someone from ARM

- Probably one other company too

Details of the event are here. There is no need to register although you must be registered for DVCon.

Immediately following the lunch, at 1.30pm in the Siskiyou ballroom, Jasper is running a tutorial Leveraging Formal Verification Throughout the Entire Design Cycle. The tutorial last until 5pm and is conducted by Lawrence Loh and Norris Ip. They will talk about the benefits of using formal technology in such areas as:

- Stand-alone verification of architectural protocols

- Designer sandbox testing for RTL development

- End-to-end data packet integrity

- SoC connectivity and integration verification

- Root-cause isolation and full proofs during post-silicon debug

Formal verification can be a valuable addition to traditional verification methods. For example, applying formal techniques early in the design cycle to exhaustively verifying block-level design functionality can produce higher quality RTL delivered to unit and system level verification. Attendees will learn about new formal technologies and flows that enable designers and verification engineers to augment existing flows. Also included will be discussions about how effort applied to one application can be leveraged in others. When applied intelligently, formal technologies can enhance traditional design and verification flows to help reduce the risks associated with increasing SoC complexity.

Details of the tutorial are here. You can add this tutorial to your DVCon pass with tutorials, or even register just to attend this one tutorial. Details of registration are here.

Using "Apps" to Take Formal Analysis Mainstream

On my last graphics chip design at Intel the project manager asked me, “So, will this new chip work when silicon comes back?”

My response was, “Yes, however only the parts that we have been able to simulate.”

Today designers of semiconductor IP and SoC have more approaches than just simulation to ensure that their next design will work in silicon. Formal analysis is an increasingly popular technology included in functional verification.

DVCon 2012

I received notice of DVCon 2012 coming up in March, and saw a tutorial session called: Using “Apps” to Take Formal Analysis Mainstream. I wanted to learn more about the tutorial so I contacted the organizer, Joe Hupcey III from Cadence and talked with him by phone.

Joe Hupcey III, Cadence

Q What is an App?

A: An app is a well documented capability or feature to solve a difficult, discreet problem. An App has to be more efficient to use (like how formal can be more efficient than a simulation test bench alone). An app has to be easy enough to use without having a PhD in Formal analysis.

Q: Who should attend this tutorial?

A: Design and verification engineers that could benefit from the use of formal. Little coaching and documentation is needed to get up to speed. Also Formal experts can benefit. Design and verification engineers that want to quickly and easily take advantage of the exhaustive verification power that formal and assertion-based verification has to offer.Formal experts that what to branch out, and make all their colleagues more productive, plus in the case of the apps they tie into the Metric-Drive Verification flows the contribution made by formal can be mapped to simulation terms.

Q: Does it matter if my HDL is Verilog, VHDL, SystemVerilog or SystemC?

A: All languages benefit from formal, PSL or SystemVerilog Assertions are talked about and used.

Q: What are the benefits of attending this tutorial?

A: Everyone on the design and verification team gets some value out of formal tools and methodology. We’ll be showing 5 or 6 apps that are available for use today. As I noted above, the “apps” approach starts with hard problems where formal, or formal and simulation together, are more efficient than simulation alone – then structures a solution that’s laser focused on the problem. There are quite a few apps available today – so if you are a Cadence customer this tutorial will help you get the most of the licenses you already have.

… plus we are hoping to include a bonus, guest speaker from a world-wide semiconductor maker who will speak about the app he created for a current project. (The engineer is working with his management to get approval now)

Our lead example app is one for SOC connectivity – we show how to validate the connectivity throughout the entire SOC, adding BIST, plus using low-power mode controls. You could create a test bench, simulate and verify that connectivity is correct (couldn’t test exhaustively all combinations). SOC Connectivity app accepts input as an Excel spreadsheet with connectivity, it then turns that into assertions, finally the Formal tool verifies that assertions are true for all cases (finds counter-examples where design fails). This takes only hours to run, not weeks to run like simulation. This is just part of the Cadence flow – assertion driven simulation is kind of unique to Cadence (take formal results, feed into coverage profile to help improve test metrics).

Q: Why should my boss spend the $75?

A: Because these apps can help save you design and verification time faster than running pure simulation alone. Case studies are use to provide measured improvements. You can leave the tutorial, go back to work, and start using the formal approaches. The main presenters are experts in each area.

Christopher Komar – Formal Solutions Architect at Cadence Design Systems, Inc.

Dr. Yunshan Zhu – Presdient and CEO, NextOp Software. They have an assertion synthesis tool that reads the TB and the RTL for the DUT, then creates good assertions (not a ton of redundant assertions). BugScope will be shown along with case studies.

Vigyan Singhal – CEO at Oski Technology, they make formal apps for both the design and verification engineers and will talk about assertion-based IP.

Source: Oski Technology

Summary

To learn more about formal analysis applied to IP and SoC design then consider attending the half-day tutorial at DVCon on March 1 in San Jose. You’ll hear from people at three different companies:

For just $75 you receive the slides on a USB drive and they provide coffee and feed you lunch.