MIPI set of specifications (supported by dedicated controllers) are completed by a PHY function, the D-PHY or the M-PHY function. The D-PHY was the first to be released, and most of the MIPI functions supported in a smartphone we are using today probably still use a D-PHY, but the latest MIPI specifications have been developed based on the M-PHY usage. Which does not means that the D-PHY will disappear any soon, but clearly M-PHY is the future…

At the early days of MIPI introduction, Synopsys was not as comfortable with MIPI as an IP product, as you could not consider the M-PHY as a “one size fits all” traditional IP product: the specification defines M-PHY Type I, Type II, and within these Type, another set of options, High Speed Gear 1, 2 and 3 for Type II and for type I the same, plus Pulse Width Modulator (PWM) 0, 1 to 7. This way to define one product, but with multiple options to be supported, was hurting Synopsys product marketing approach, which is to develop one product, and address a market as wide as possible using a large sales force… this is in fact the definition of an IP business!

The discussion I had last week with Navraj Nandra, Marketing Director for Mixed-Signal IP (including the PHY Interfaces product line), shows that Synopsys has found a way to solve this business issue with an elegant engineering solution: the MIPI M-PHY developed by Synopsys in 28nm is a modular product. If a customer needs to implement the M-PHY Type II supporting Gear 1 to 3, he will integrates this function only. This is the best way to optimize the associated footprint and power consumption, and it is easier than to follow the other potential route which was to engage an IP or design service company to specifically develop the function supporting the part of M-PHY specification to be supported.

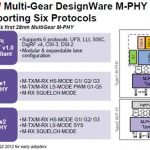

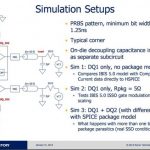

Because at Semiwiki we try to do some evangelization, let’s see what are the functional (specific) specifications associated with the M-PHY (agnostic by nature). I strongly engage you to have a look at the above picture!

At first, let’s start with the “pure” MIPI specifications, in that sense that these have been developed by the MIPI Alliance alone:

- DigRF v4 is the specification allowing to interface with RF chip (supporting LTE), can be connected directly to the M-PHY.

- Low Latency Interface (LLI) can also be connected directly to the M-PHY. We will come back later in this paper to LLI, as the release 1.0 has been announced this week, at MWC

- CSI-3, the Camera Interface, has to be connected through UniPro, an “agnostic” controller, to the M-PHY

- DSI-2, the Display Interface, connect to the M-PHY also through UniPro

- Universal Flash Storage (UFS), a specification jointly developed by JEDECand MIPI, to support external Flash devices (Card), also connect through UniPro

- Finally, another specification has been jointly developed, with USB-IF, called SuperSpeedIC (SSIC), allowing to connect two USB 3.0 compatible devices, directly on a board (no USB cable)

To summarize, M-PHY and UniPro are agnostic technical specifications (one mixed-signal, the other digital), and CSI-3, DSI-2, DigRF v4, LLI, SSIC and UFS are function specific specifications, defined by MIPI Alliance alone, or by MIPi Alliance and USB-IF, or JEDEC for respectively the last two.

MIPI has the potential, from a technical standpoint, thanks to the benfits it brings in term of High Speed Serial AND low power Interface, and in term of interoperability, to be used in PC, Media Tablet and Consumer Electronic segments, on top of the Wireless handset segment. MIPI Alliance has the willingness to support such a pervasion, but doing some evangelizationwill be necessary for the MIPI specifications to go to the mainstream, Consumer electronic or OC segments!

LLI Specification has been officially released by the MIPI Alliance, at the occasion of the Mobile World Congress in Barcelona, this week. As indicated by the name, the round-trip latency of the LLI inter-chip connection is fast enough for a mobile phone modem to share an application processor’s memory while maintaining enough read throughput and low latency for cache refills. Sharing the same DRAM device means the wireless handset integrator can save real estate printed circuit board (PCB) space and create a thinner smartphone, or implement additional device, more features to the smartphone, like NFC chip for example. It also means that the OEM will save, on every manufactured smartphone, the cost of one DRAM ($1 to 2$). If you manufacture dozen of million smartphone like some of the leaders, you can see how quickly you will get the return on the initial investment done by the chip makers to acquire the IP!

MIPI Alliance is strongly supportive of LLI, as we can see from this quote: “As active MIPI contributors, Synopsys and Arteris are aiding in the adoption of the MIPI M-PHY and MIPI Low Latency Interface,” said Joel Huloux, chairman of the board of MIPI Alliance. “The early integration and availability of the Arteris and Synopsys solution helps speed time to market for MIPI LLI adopters.” LLI support from Arteris and Synopsys illustrate how important is to build a strong partnership when selling a complementary solution, as the joint solution consists of Arteris’ Flex LLI™ MIPI LLI digital controller IP and Synopsys’ DesignWare® MIPI M-PHY IP. A team of Arteris and Synopsys engineers, formed to facilitate verification and testing of the joint solution, validated its functionality and interoperability.

And for those who love to get insights, you should know that LLI was initially developed by an Application Processor chip maker, who understood that the function, to be successful on the market, has to be marketed and sold by an IP vendor, Arteris was selected as they were already marketing C2C or “Chip To Chip Link” IP, offering exactly the same functionality (sharing a DRAM between Modem and Application Processor), by the means of a parallel Interface in this case, but we will come back soon about this IP.

Eric Esteve – See “MIPI IP Survey & Forecast” from IPNEST