Modern microprocessor and memory designs often have hundreds of datapaths that traverse the width of the chip, many of them very wide (over one thousand signals). To meet signal timing and slope targets for these buses, designers must insert repeater cells to improve the speed of the signal. Until now, the operations associated with managing large numbers of large buses have been manual: bus planning, bus routing, bus interleaving, repeater cell insertion and so on. However, the large and growing number of buses, especiallly in multi-core microprocessor designs, means that a manual approach is both too slow and too inaccurate. So Pulsic have created an automated product to handle this increasingly critical task, Unity Bus Planner.

Another problem that automation helps to address is that the first plan is never the last. As von Clausewitz said: “No campaign plan survives first contact with the enemy”. In just the same way, no bus plan survives once the detailed placement of the rest of the chip gets done. Repeater cells, since they involve transistors, don’t fly over the active areas but have to interact with them, so as the detailed layout of the chip converges the bus plan has to be constantly amended.

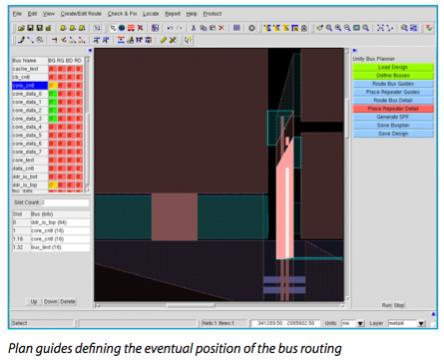

During the initial floorplanning stage, designers do block placement and power-grid planning followed by initial bus and repeater planning. Buses that cross the whole chip need to be carefully planned. At the end of this stage initial parasitic data is available for simulating critical parts of the design.

During the initial floorplanning stage, designers do block placement and power-grid planning followed by initial bus and repeater planning. Buses that cross the whole chip need to be carefully planned. At the end of this stage initial parasitic data is available for simulating critical parts of the design.

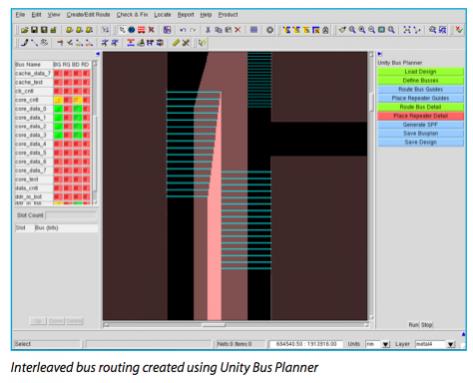

During bus planning itself, designers fit as many buses as possible through dedicated channels to avoidtiming issues. Very fast signals require shielding with DC signals such (such as ground) to prevent crosstalk noise issues. Often architects interleave buses so that they provide shielding for each other rather than using valuable resources for dedicated shielding. But planning, interleaving and routing hundreds of very wide buses is slow and error-prone. Internal tools created to do this are often unmaintainable and inadequate for the new generation of still larger chips.

Signals on wide buses need to arrive simultaneously with similar slopes so that they can be correctly latched. This means that the paths must match in terms of metal layers, vias, repeater and so on, a very time consuming process, especially when changes inevitably need to be made as the rest of the design is completed.

With interactive and automated planning, routing and managment, designers can complete bus and repeater-cell planning in minutes or hours rather than days or weeks. Automation also makes the inevitable subsequent modifications faster and more predictable.

With interactive and automated planning, routing and managment, designers can complete bus and repeater-cell planning in minutes or hours rather than days or weeks. Automation also makes the inevitable subsequent modifications faster and more predictable.

The Unity Bus Planner product page is here.

Musk’s Orbital Compute Vision: TERAFAB and the End of the Terrestrial Data Center