Who makes the decision and declare that a specific interface protocol is successful? Not me, as I can only consolidate market share data and some insight information coming from the industry. The end user, when going to a shop (real or virtual) and spend a significant part of his budget to buy an electronic product, selecting among hundreds, will eventually decide for the success of a certain feature (SuperSpeed USB, HDMI or ThunderBolt). But, if you wait for the success of this feature on the mainstream market to integrate it into your system (OEM), your SoC (chip maker) or your IP portfolio (EDA/IP vendor), then you are respectively 12/18 months, 2 years or more late…

How to best forecast a specific protocol adoption? One option is to look at the various IP sales, it will give you a good idea of the number of SoC or IC offering this feature on the market in the next 12 months. Once again, if you wait for the IP sale to have reached a maximum, it will be too late, so you have to monitor the IP sales dynamic when the sale volume is still in the low range to make an efficient analysis, which can help you taking the right decision just a little bit in advance in respect with your competitor – to benefit from a Time-To-Market advantage. That’s why we will mention the clear winners, demonstrating high market penetration (and becoming “de facto” standard in certain market segments), and also put the focus on the emerging protocols demonstrating fast growing penetration.

The winners in 2012

HDMI is again this year the most successful protocol, both in term of market penetration in the Consumer/HDTV segment and in term of pervasion in various segments like PC, Wireless Handset (smartphone), Set-Top-Box, DVD players and recorders, Digital Video Camera and more. Analyst consensus is that almost 3 billion HDMI ports have been shipped since the inception (2004 for the protocol definition, 2006 for the first devices shipped in the market). If we look at the protocols in direct competition with HDMI, we find only DiiVa, released in China in 2010 and aiming to escape paying royalties to Silicon Image while providing the same bandwidth, but the adoption rate for DiiVa has been close to null. DisplayPort has become complementary to HDMI, the adoption has been confirmed in 2012, after a strong growth in 2011: the protocol is well tailored for interfacing a PC and a screen, that’s naturally here that the adoption is high. We clearly rank DisplayPort in the winner list.

It will be interesting to monitor the adoption for “Mobile High-Definition Link” (MHL), another creation from Silicon Image, teaming with Nokia, Sony, Samsung and xxx, which provide the same bandwidth capability (and compatibility) that HDMI… but with a micro-USB (5 pin) connector instead of the traditional HDMI connector. Vendors should always take care about connectors! Customer need it to interface with other products, but vendor are reluctant to integrate too many of these (because of over-cost and form factor). MHL allows OEM to integrate a single connector, micro-USB, to support two interfaces: HDMI and USB 2.0. Samsung is integrating 11 pin micro USB, allowing using HDMI and USB 2.0 at the same time, which is even better. You can bet that chip makers, OEM and end users will like it! Just keep in mind that MHL will be primarily used in mobile electronic systems, smartphones, media tablet and probably notebook and ultrabook PC. That will make only one BILLION potential devices to integrate MHL in 2013…

MIPI is a set of interface specifications (not a standard according with the MIPI Alliance), initially specifically tailored for wireless phones system, defining almost any kind of chip to chip interface: Camera to Application Processor (AP) with CSI, Display with AP (DSI), Baseband with AP (Low Latency Interface, allowing to share an external DRAM), main SoC with RF chipset (DigRF) and another dozen specifications. Even if an end user will probably ignore that his smartphone has “MIPI inside”, MIPI brings major advantages:

- OEM can source functional chips (for example Camera controller or RF chipset) from multiple vendors, to build a unique system, being confident about H/W interoperability: multiple sourcing made easier

- OEM can follow the major trend of the 2010s, offering higher and higher bandwidth for even more data (image, video, raw data) exchange, using a multi gigabit/s PHY and related controller, specifically tailored for low power. Because power consumption has replaced in the 2010s the pure performance (MIPS) of the 2000s, MIPI is one of the door opener for chip penetration in mobile application

- End user will eventually benefit from “MIPI inside”, because Electronic systems could use cheaper IC: interoperability is offering higher level of competition, and prevent Intel-like monopolistic position, in conjunction with the availability of ARM architecture to any chip maker.

- End user is benefiting today from mobile electronic devices (smartphone, media tablet) with longer than ever battery life coupled with impressive CPU and GPU performance, thanks to huge engineering effort to design for low power, the low power nature of ARM architecture, advanced technology nodes usage… and MIPI set of specification!

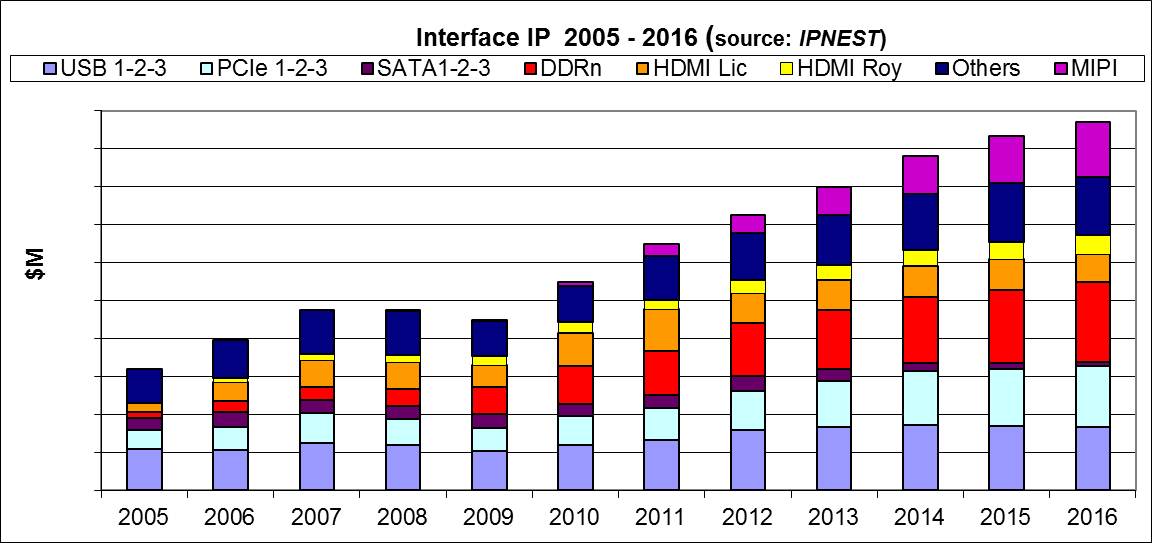

I am happy to share with Semiwiki readers an extract of “Interface IP Survey”, showing actual data about MIPI IP market, exhibiting 300% year to year growth rate… just keep in mind that these data only represent MIPI IP external sourcing, which is only a small part of the total MIPI function integrated by chip makers, are most of the large companies tend to use internally designed IP.

To give a complete picture about MIPI, it’s important to notice that the MIPI Alliance has not only continue to finalize specifications in 2012 (like Battery Interface), but also consolidate MIPI positioning within the Interface Ecosystem, by concluding very promising agreements with no less than three standard organizations:

- JEDEC: definition of Universal Flash Storage (UFS), to be used in conjunction with MIPI M-PHY, offering within a mobile system

- USB-IF: specification of SuperSpeed USB Inter Chip (SSIC), where the USB 3.0 PHY can be replaced by MIPI M-PHY, offering high bandwidth and low power capabilities for chip to chip communication in a mobile system

- PCI-SIG: definition of “Mobile Express”, delivering an adaptation of the PCI Express® (PCIe®) architecture to operate over the MIPI M-PHY® physical layer technology

We will use these agreements to introduce the next two Interface protocol winners: USB 3.0 and PCI Express.

The very first USB 3.0 forecast built by IPNEST was done in 2009. At that time, I (and many IP vendors investing into the development of SSUSB IP) was expecting the technology take off during 2010 and strong IP sale to be induced. Unfortunately, we were just neglecting one piece of the puzzle, even if it was a big one: Intel. Just because Intel decided to delay, and delay again the integration of USB 3.0 function into their PC chipset. The only way to see SSUSB supported into a PC was marginal in 2010, then 2011 and part of 2012, as PC integrators had to insert a PCIe to USB 3.0 bridge IC (from NEC)… And the technology did not take off in 2010, 2011 and even in 2012.

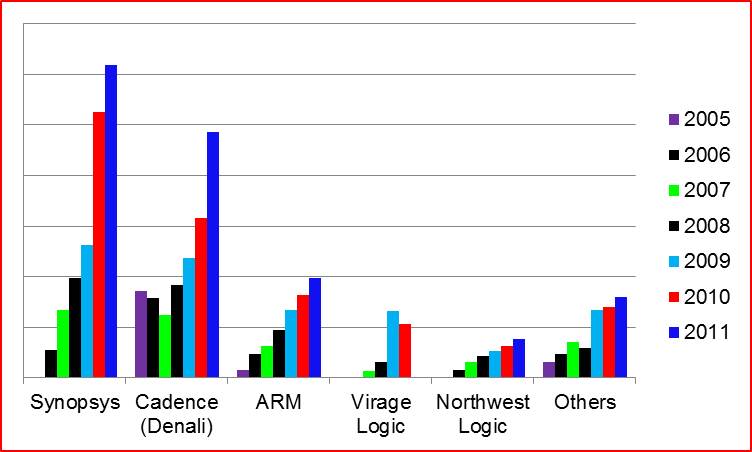

The status has now changed (should I say thanks to Intel for integrating SSUSB in their chipset in mid-2012?) and SuperSpeed USB IP have started selling well during 2012, with a design start count being in 2012 equal to the sum of design starts during 2009, 2010 and 2011. In the meantime, many IP vendors have given up (PLDA, Snowbush to name a few), and the result is that there is a clear, undisputed winner in the USB 3.0 market: Synopsys!

The company was already ultra-dominant on the traditional USB IP market, Chipidea acquisition in 2010 bringing over 90% market share. Because SuperSpeed USB specification is calling for both HSUSB and USB 3.0 support, most of the market will go to the safer solution, and choose for SSUSB the IP vendor already strong in previous USB specification. We will address this specific IP market segment more in depth in a future article, so stay tuned!

PCI Express penetration has started in 2005 and has never stopped since then. The technology can be used in many, many market segments, with the notable exception of Consumer Electronic and mobile wireless. In 2005, PCIe gen-1 was used, delivering 2.5 GT/s and per lane (2 Gbit effective), and in 2012 PCIe gen-3 was going mainstream in the PC segment, delivering 4X effective bandwidth per lane compared to the first generation. Such a status would allow ranking PCI Express in the winner protocols, in fact PCIe success will go even further, as at the end of 2011, SATA-IO Organization has decided to offer ‘SATA Express”, the Non Volatile Memory storage application interface will be supported by NVM Express and in 2012 MIPI Alliance has defined “Mobile Express”.

SATA Express simply means that, for PHY specification higher than 6 GT/s, chip makers will integrate PCI Express as transport protocol (PCIe Controller and PCIe PHY) and that SATA will be exercised at the S/W level. In other words, the last pure SATA PHY specification was SATA 3 offering 6 GT/s, any speed above 6 Gbs could be supported by PCIe. That clearly indicates that SATA protocol is a loser for individual storage, but also Fiber Channel (replaced by PCIe) for the massive storage applications.

Non Volatile Memory is a technology, not a protocol, but the availability of lower cost Solid State Disk (SSD) allowing the penetration of NVM into consumer PC for storage has obliged to offer the related protocol to interface with SSD: NVM Express. Again PCIe protocol will be used for transport, the NVM specific management features being added/merged with PCIe.

It’s possible to find a PR for Mobile Express, but no picture when scanning the web. This just means that, if Mobile Express is a very promising technology, allowing reusing PCIe based application in a mobile electronic system, benefiting from the low power consumption of MIPI M-PHY physical layer, it’s too early today to see Mobile Express based applications. The fact that MIPI M-PHY is still specified at 2.9 Gbps maximum could be one of the reasons, and we expect the next generation M-PHY specification (5.8 Gbps) to be released in 2013, so it’s just a question of imagination, and I officially send a “Call for Mobile Express Application” here!

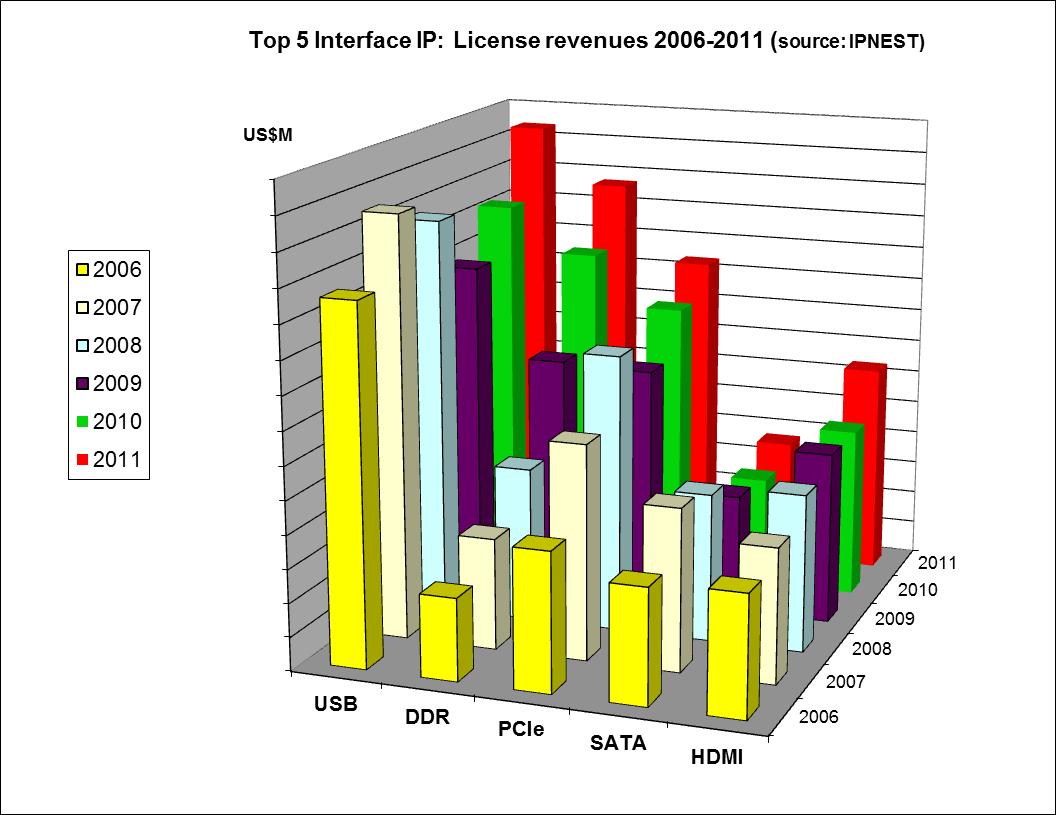

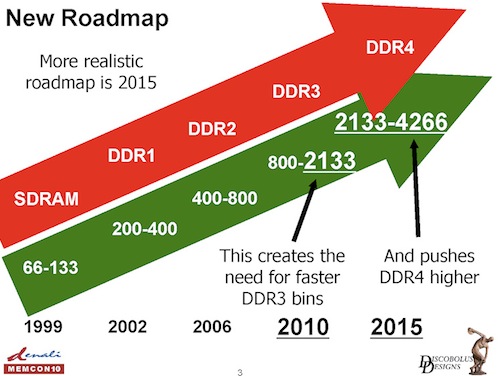

Another protocol is seeing a wide adoption, and very fast growing IP sales: DDRn. DDRn controller is a mean to interconnect a SoC with memory, using a digital part (Controller) and a physical media access (PHY), so it’s built like every other modern high speed protocol. We have shown in the “Interface IP Survey” that, even if the ASIC design starts decline year after year, the SoC proportion of these design start is growing higher.

Because there is more SoC design starts, a SoC being defined as a chip integrating one or more processor (CPU, GPU, DSP, and Microcontroller), the net number of DDRn controller is growing at the same rate. Because the DDRn controller design from scratch is becoming more difficult to manage with DRAM frequency increase, leading to move from ‘Soft PHY” to hardened PHY for example, the move to external sourcing of DDRn controller IP is growing faster than any other Interface IP.

This looks theory, but we can see effective sales of DDRn controller IP growing on line with the theory! Just look at these results from IPNEST for 2005-2011… DDRn IP segment is strongly growing, and the leadership is split between Synopsys (again), Cadence (thanks to Denali acquisition) and ARM.

… and thelosers in 2012

I think that most of you are now suspecting who are the losers, don’t you?

ThunderBolt, has been developed and promoted by Intel and adopted by Apple, to be used in the high end PC segment. It looks like end users have been warned by the (defunct?) WinTel duopoly, so when they see:

They feel:

Whatever the reason, ThunderBolt will not replace SSUSB, neither HDMI or MHL, it will be a complementary protocol, that chip makers can NOT integrate as any other IP function (HDMI, PCIe, MIPI and so on) as Intel will decide who to license the technology, and only in a standalone ASSP, not as an IP function. As far as I am concerned, being IP-minded, I am pretty happy to see the un-success of ThunderBolt!

We have seen that current HDD based storage application could be supported by SATA Express, and future HDD based storage with interface frequency (stricktly) higher than 6 Gbps have to rely on PCI Express transport protocol, as no SATA physical layer has been specified by SATA-IO above 6 Gbps. Moreover, SSD is the future of storage in the consumer market, and NVM Express (not SATA) has been defined as the transport protocol for NVM based SSD. SATA as a transport protocol will simply die, the question is just how long it will take…

DIIVA was a tentative to kick out HDMI from the (Chinese?) consumer market. The goal was challenging, so the result is not really disappointing, it just reflect that end user has the final cut, when dealing with a protocol to be used in consumer electronic. You can try to impose a protocol standard, but a kind of democratic effect will take place, let’s call it the market feedback…

Last… but not least, the unexpected winner

Network on Chip (NoC) is not a protocol, neither an interface, rather an interconnect function, buried into a SoC, to connect, manage and monitor the multiple IP blocks. As such a NoC will be, by definition, connected to all the interface functions, from DDRn memory controller to USB, PCIe, UFS and so on. That we have seen in 2011-2012 is the strong penetration of NoC IP into various market segments (Wireless, Consumer Electronics, Automotive and more), although the NoC was at concept stage in the mid-2000. This trend has been so effective that a NoC IP vendor like Arteris has multiplied revenue coming from upfront licenses by 3 in 2011 (compared with 2010), and the growth is going on in 2012, probably not at the same rate, but sustained.

That is, why not imagine that, at the end of the 2010’s, a cleaver IP vendor would sell the NoC packaged together with most of the Interface IP? This would be not only the “one-stop-shop” concept, but the “All-in-One” Interface/Interconnect IP function… Maybe Kurt Shuler, VP of Marketing with Arteris would like to comment this assertion. Feel free to do it here!

Eric Esteve– from IPNEST –

If you want to know more about “Interface IP Survey”, just go here

Musk’s Orbital Compute Vision: TERAFAB and the End of the Terrestrial Data Center