When I started dabbling in hardware again for fun using Arduinos about five years ago, it had been a long time since I had played with microprocessor chips. The epiphany for me was seeing how easy it was to load programs onto the onboard flash on something like an Atmel AVR using the SPI interface. My previous experience decades early… Read More

Tag: interface

CEO Insight: Transformation of Vayavya Labs into System Design Automation

With the advent of SoCs, design abstractions and verification has moved up at the system level. It’s imperative that EDA moves up the value chain to start design automation at system level. The System Design Automation will be the new face of EDA in coming years.… Read More

HW/SW Interfaces for Portable Stimulus

With growing size and complexity of SoC, the semiconductor community is realizing the growing pain of verification. The cost of SoC verification grows exponentially with design size. Moreover, there is no single methodology for verifying a SoC; multiple engines are used in different contexts through different verification… Read More

Advances in DDR IP Solution for High-Performance SoCs

In this era of high-performance, low-power, and low-cost devices coming up at an unprecedented scale, the SoCs can never attain the ultimate in performance; always there is scope for improvement. Several methods including innovative technology, multi-processor architecture, memory, data traffic management for low latency,… Read More

Configurable System IP from a Tool Provider

While I have previously blogged on Forte’s Cynthesizer Workbench’s Interface Generator, I want to take another look from a different perspective. Watching the tool and IP together in action through public videos provided by Forte it struck me as odd what I did not consider earlier, on what should have been obvious to me – Forte is… Read More

Reduce Errors in Multi-threaded Designs

Many advanced algorithmic IPs are described in C++. We use this language because of its flexibility. Of course software algorithms are written to be executed on processors so they don’t solve all the issues of getting the algorithm implemented in hardware directly. This is not simply a high-level synthesis (HLS) issue. Usually… Read More

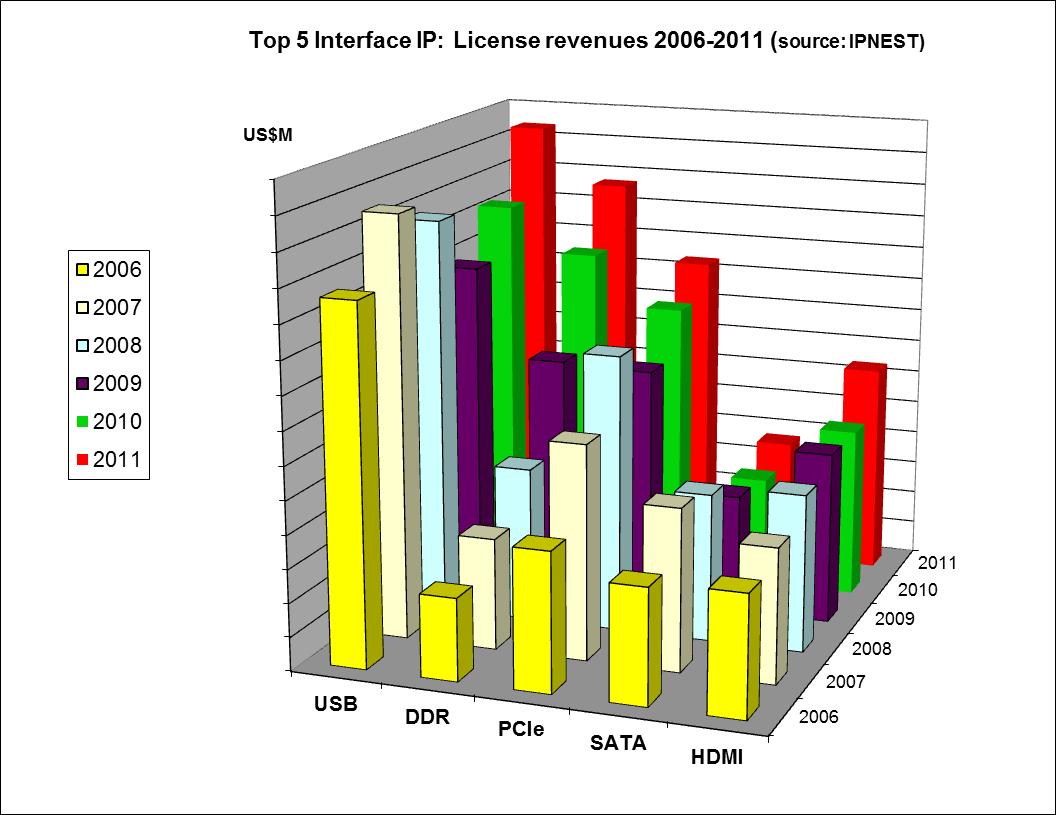

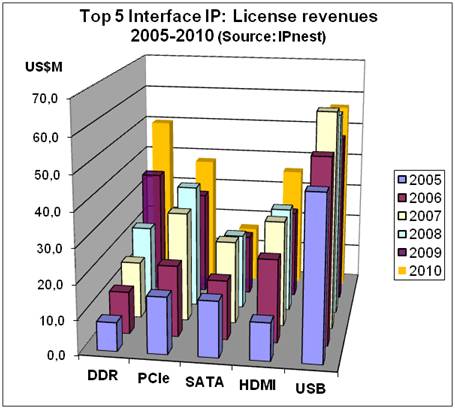

Interface Protocols, USB3, PCI Express, MIPI, SATA… the winners and losers in 2012

Who makes the decision and declare that a specific interface protocol is successful? Not me, as I can only consolidate market share data and some insight information coming from the industry. The end user, when going to a shop (real or virtual) and spend a significant part of his budget to buy an electronic product, selecting among… Read More

A tribute to Research on Interface IP Market

Denali acquisition by Cadence in May 2010, ChipIdea, Virage Logic, and nSys acquisitions by Synopsys in 2009, 2010 and 2011 (resp.) shows that IP market is consolidating… but new IP vendors are still emerging! So we need to know on which product the Interface IP market leader will tend to a dominant position, which new products… Read More