You are currently viewing SemiWiki as a guest which gives you limited access to the site. To view blog comments and experience other SemiWiki features you must be a registered member. Registration is fast, simple, and absolutely free so please,

join our community today!

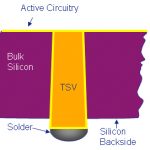

3D IC design and what has come to be known as 2½D IC design, with active die on a silicon interposer, require new approaches to verification since the through silicon vias (TSVs) and the fact that several different semiconductor processes may be involved create a new set of design challenges

The power delivery network is a challenge… Read More

I attended much of the Jasper users’ group a week ago. There were several interesting presentations that I can’t just blog about because companies are shy, and some that would only be of interest if you were a user of Jasper’s products on a daily basis.

But for me the most interesting presentations were several… Read More

Noise Couplingby Paul McLellan on 10-24-2011 at 8:47 amCategories: Ansys, Inc., EDA

One of the challenges of designing a modern SoC is that the digital parts of the circuit are really something that in an ideal world you’d keep as far away from the analog as possible. The digital parts of the circuit generate large amounts of noise, especially in the power supply and in the substrate, two areas where it is impossible… Read More

The mobile devices market is simply exploding, with smartphones shipmentgoing up to the sky, tabletsemerging so fast that some people think it will replace PC (but this is still to be confirmed…). This lead mobile SoC designs to integrate increasingly more features, to support customer needs for more computing power and sophisticated… Read More

In working with TSMC and GlobalFoundries on AMS design reference flows I have experienced first hand the increasing verification challenges of nanometer analog, RF, and mixed-signal circuits. Tools in this area have to be both silicon accurate and blindingly fast! Berkeley Design Automation is one of the key vendors in this … Read More

Even if nSys acquisition by Synopsys will not have a major impact on Synopsys’ balance sheet, it is a kind of earthquake in the Verification market landscape. After the Denali acquisition by Cadence in 2010, nSys was most probably the market leader in verification IP, if we look at the independent VIP providers (excluding Cadence).… Read More

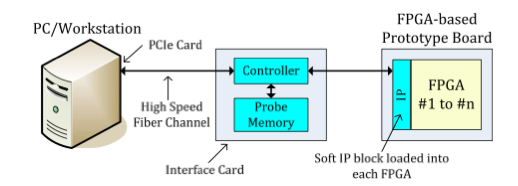

It is no secret that SoC designs continue to increase in complexity and time-to-market windows are shrinking. While there is room for debate on just how big a fraction of SoC design effort goes on verification, there is no debating that it is a large part of the total. Simulation is increasingly too slow, especially when software … Read More

At DAC Jasper presented a seminar with ARM on cache coherency and verification of cache coherency. The seminar is now available online for those of you that missed DAC or missed the seminar itself.

Cache architectures, especially for multi-core architectures, are getting more and more complex. Techniques originally pioneered… Read More

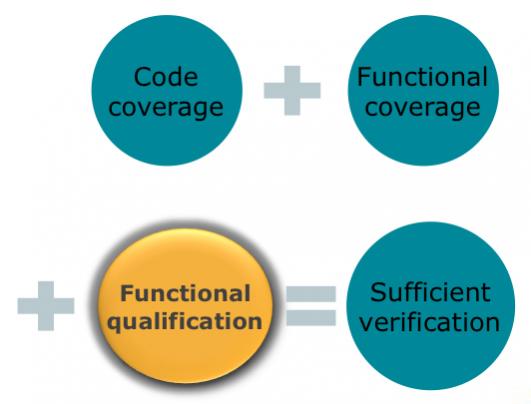

The traditional way for analyzing the effectiveness of testing in the software world and in the RTL world is code coverage. Make sure that every line of code is executed. This is a pretty crude measure since even 100% code coverage doesn’t mean that all the condition has really been tested but it is certainly necessary–after… Read More