You are currently viewing SemiWiki as a guest which gives you limited access to the site. To view blog comments and experience other SemiWiki features you must be a registered member. Registration is fast, simple, and absolutely free so please,

join our community today!

It’s a matter of pride to me and many others from Atrenta days that the brand we built in SpyGlass has been so enduring. It seems that pretty much anyone who thinks of static RTL checking thinks SpyGlass. Even after Synopsys acquired Atrenta, they kept the name as-is, I’m sure because the brand recognition was so valuable.

Even good… Read More

I think Synopsys would agree that they were not an early entrant to the emulation game, but once they really got moving, they’ve been working hard to catch up and even overtake in some areas. A recent webinar highlighted work they have been doing to overcome a common challenge in this area. Being able to boot a billion-gate design, … Read More

Verification coverage is a tricky concept. Ideally a definition would measure against how many paths were tested of every possible path through the complete state graph, but that goal is unimaginably out of reach for any typical design. Instead we fall back on proxies for completeness, like hitting every line in the code. This … Read More

When I worked at Intel designing custom chips my management would often ask me, “Will first silicon work?” My typical response was, “Yes, but only for the functions that we could afford to simulate before tape-out.” This snarky response would always cause a look of alarm, quickly followed by a second … Read More

I’ve owned and used many generations of cell phones, starting back in the 1980’s with the Motorola DynaTAC phone and the biggest usability factor has always been the battery life, just how many hours of standby time will this phone provide and how many minutes of actual talk time before the battery needs to be recharged… Read More

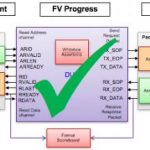

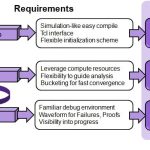

Formal verification can provide a large productivity gain in discovering, analyzing, and debugging complex problems buried deep in a design, which may be suspected but not clearly visible or identifiable by other verification methods. However, use of formal verification methods hasn’t been common due to its perceived complexity… Read More

We might wish that all our design automation needs could be handled by pre-packaged vendor tool features available at the push of a button, but that never was and never will be the case. In the language of crass commercialism, there may be no broad market for those features, even though you consider that analysis absolutely essential.… Read More

Synopsys hosted a lunch session on Thursday of DVCon. Michael Sanie of Synopsys opened the session, with a look back at the last DVCon where he had talked about Verification Compiler (VC) and extending the platform to Verification Continuum, which adds emulation and FPGA-based prototyping (HAPS – there was a very cool HAPS demo… Read More

I met Michael Sanie last week. He is in charge of verification marketing at Synopsys. I know him well since he worked for me at both VLSI Technology and Cadence. In fact his first job out of college was to take over support of VLSIextract (our circuit extractor), which I had written. But we are getting ahead.

Michael was born in Iran and… Read More

Usually, we get the incremental story in news: this new release is x percent better at this or that than the previous release, and so on. Often missing is the big picture, telling how the pieces all tie together. Synopsys took on that challenge in their latest FPGA-based prototyping webinar. … Read More