Verific is an unusual company. They are completely dominant in what they do – providing parsers for Verilog/SV, VHDL and UPF. Yet they have no ambition to expand beyond that goal. Instead, per Michiel Ligthart (President and COO), they continue to “sharpen the saw”. This is an expression I learned in sales training, habit #7 from… Read More

Tag: upf

Webinar – How to manage IP-XACT complexity in conjunction with RTL implementation flow

Standards help our EDA and IP industry grow more quickly and with less CAD integration efforts, and IP-XACT is another one of those Accellera standards (1685-2009) that is coming of age, and enabling IP reuse for SoC design teams. Here at SemiWik, we’ve been writing about Defacto Technologies and their prominent use of IP-XACT… Read More

Probing UPF Dynamic Objects

UPF was created to go beyond what HDL can do for managing on-chip power. HDLs are agnostic when it comes to dealing with supply & ground connections, power domains, level shifters, retention and other power management related elements of SoCs. UPF fills the breach allowing designers to specify in detail what parts of the design… Read More

Does IDE Stand for Integrated Design Environment?

As regular readers may know, every few months I check in with Cristian Amitroaie, CEO of AMIQ EDA, to see what’s new with the company and their products. In our posts so far this year we’ve focused on verification, and now I’m wondering how an integrated development environment (IDE) provides benefits to designers. They work on huge… Read More

Low Power and RISC-V Talks at DAC2020, Hosted by Mentor

I’m going to get to low power and RISC-V, but first I’m trying out virtual DAC this year. Seems to be working smoothly, aside from some glitches in registration. But maybe that’s just me – I switched email addresses in the middle of the process. Some sessions are live, many pre-recorded, not quite the same interactive experience… Read More

The Moving Target Known as UPF

As if engineers did not have enough difficulty just getting everything right so that their designs are implemented functionally correct, the demands of lowering power consumption require changes that can affect functionality and verification. Techniques such as power gating, clock gating, mixed supply voltage, voltage … Read More

Synopsys Low Power Workshop Offers Breadth and Depth

Synopsys seems to particularly excel at these events, whether in half-day tutorials at conferences or, as in this case, in a full-day on-site workshop. You might think there’s not much that can be added in this domain, other than to bring low-power newbies up to speed, but you’d be wrong. This event set the stage with surveys on needs… Read More

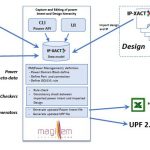

Magillem offers a practical UPF power flow

We already know that IP-Xact is extremely useful for managing IP and SOC design specifications, yet it may come as a surprise to learn that it also can be used to form the basis of a power flow too. There are design tools that read UPF to help implement and verify designs, however it can be extremely useful to understand the interplay … Read More

Foundational Excellence in a Laid-Back Style

I recently had a call with Rob Dekker, Founder and CTO of Verific. If you’re in EDA or semiconductor CAD, chances are high that you know who they are. They’re king of the hill in parser software for SystemVerilog and VHDL. When you hear a line like that, you assume a heavy dose of marketing spin, but here it really is fact. I don’t know of… Read More

CEO Interview: Cristian Amitroaie of AMIQ EDA

AMIQ EDA has caught my attention over the last few months. My first impression was that this was just another small IDE company trying to compete with established and bundled IDEs from the big 3, a seemingly insurmountable barrier. This view was challenged by an impressive list of testimonials, not just from the little guys but also… Read More