SoC integration offers huge benefits through reduced chip count in finished systems, higher performance, improved reliability, etc. A single die can contain billions of transistors, with multiple processors and countless subsystems all working together. The result of this has been rapid growth of semiconductor content … Read More

Tag: tessent

Observation Scan Solves ISO 26262 In-System Test Issues

Automotive electronic content has been growing at an accelerating pace, along with a shift from infotainment toward mission critical functions such as traction control, safety systems, engine control, autonomous driving, etc. The ISO 26262 automotive electronics safety standard evolved to help ensure that these systems… Read More

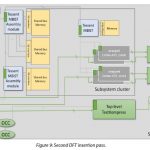

Mentor Offers Next Generation DFT with Streaming Scan Network

Design for test (DFT) requires a lot of up-front planning that can be difficult to alter if testing needs or performance differ from initial expectations. Hierarchical methodologies help in many ways including making it easier to reduce on chip resources such as the number of test signals. Also, hierarchical test allows for speed-ups… Read More

Getting Physical to Improve Test – White Paper

One of the most significant and oft repeated trends in EDA is the use of information from layout to help drive other parts of the design flow. This has happened with simulation and synthesis among other things. Of course, we think of test as a physical operation, but test pattern generation and sorting have been netlist based operations.… Read More

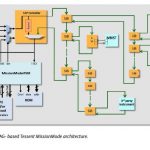

Novel DFT Approach for Automotive Vision SoCs

You may have seen a recent announcement from Mentor, a Siemens business, regarding the use of their Tessent DFT software by Ambarella for automotive applications. The announcement is a good example of how Mentor works with their customers to assure design success. On the surface the announcement comes across as a nice block and… Read More

DFT Innovations Come from Customer Partnerships

There is an adage that says that quality is not something that can be slapped on at the end of the design or manufacturing process. Ensuring quality requires careful thought throughout development and production. Arguably this adage is more applicable to the topic of Design for Test (DFT) than almost any other area of IC development… Read More

Bringing Hierarchy to DFT

Hierarchy is nearly universally used in the SoC design process to help manage complexity. Dealing with flat logical or physical designs proved unworkable decades ago. However, there were a few places in the flow where flat tools continued to be used. Mentor lead the pack in the years around 1999 in helping the industry move from … Read More

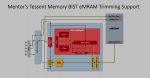

Full Solution for eMRAM Coming in 2020

It’s amazing to think that Apollo moon mission used computers that were based on magnetic core memories. Of course, CMOS memories superseded them rapidly. However, over the decades since, memory technologies have advanced significantly, in terms of density, power and new types of technologies, e.g NAND Flash. Ever since the… Read More

Automotive Market Pushing Test Tool Capabilities

It’s easy to imagine that the main impetus for automotive electronics safety standards like ISO 26262 is the emergence of autonomous driving technology. However, even cars that do not offer this capability rely heavily on electronics for many critical systems. These include engine control, braking, crash sensors, and stability… Read More

Hierarchical RTL Based ATPG for an ARM A75 Based SOC

Two central concepts have led to the growth of our ability to manage and implement larger and larger designs: hierarchy and higher levels of abstraction. Without these two approaches the enormous designs we are seeing in SOCs would not be possible. Hierarchy in particular allows the reuse of component blocks, such as CPU cores.… Read More