Networks-on-chip (NoCs) are very configurable, arguably the most configurable piece of IP that you can put on a chip. The only thing that comes close are highly configurable extensible VLIW processors such as those from Tensilica (Cadence), ARC (Synopsys) and CEVA but Sonics would argue their NoCs are even more flexible. But … Read More

Tag: systemverilog

Cadence & ARM Optimize Complex SoC Performance

Now a day, a SoC can be highly complex, having 100s of IPs performing various functionalities along with multi-core CPUs on it. Managing power, performance and area of the overall semiconductor design in the SoC becomes an extremely challenging task. Even if the IPs and various design blocks are highly optimized within themselves,… Read More

Because X doesn’t always mark the exact spot

Digital hardware has a habit of deciding – based on the bias and behavior of transistors – to drive outputs to a 0, or a 1, or if commanded a high-impedance Z state. SystemVerilog recognizes a fourth state: X, the “unknown” state a simulator has trouble inferring.

Simulators have a choice. Under X-optimism, they can convert the unknown… Read More

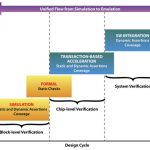

Assertions verifying blocks to systems at Broadcom

Speaking from experience, it is very difficult to get an OEM customer to talk about how they actually use standards and vendor products. A new white paper co-authored by Broadcom lends insight into how a variety of technologies combine in a flow from IP block simulation verification with assertions to complete SoC emulation with… Read More

Constrain all you want, we’ll solve more

EDA tool development is always pushing the boundaries, driven in part by bigger, faster chips and more complex IP. For several years now, the trend has been developing tools that spot problems faster without waiting for the “big bang” synthesis result that takes hours and hours. Vendors, with help from customers, are tuning tools… Read More

Debugging Verification Constraints

In his DAC keynote last year (2012) Mike Mueller of ARM compared how much CPU was required to verify the first ARM versus one of the latest ARM Cortex CPUs. Of course the newer CPU is hundreds of times larger than the first ARM but the amount of verification required was millions of times as much, requiring ARM to construct their own datacenter… Read More

Training Day at DAC

This year for the first time the Thursday of DAC is tranining day. So that would be June 6th in Austin, of course. There are four tracks of training focused on SystemC, ARM Cortex and two on SystemVerilog, all areas of increasing use in SoC design, especially in mobile.

Each track of training is divided into two parts, one held from 9am… Read More

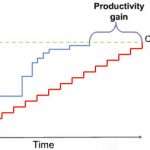

Multi-level abstraction accelerates verification turnaround

Often a question is raised about how SystemC improves verification time when the design has to go through RTL in any case. A simple answer is that with SystemC, designs can be described at a higher level of abstraction and then automatically synthesized to RTL. When the hands-on design and verification activity is at a higher level,… Read More

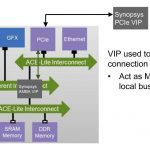

Happy Birthday to Synopsys VIP

I met Mike Sanie around DVCon time and planned to write a blog about the one year anniversary of Synopsys Discovery VIP which was announced during Aart’s keynote at DVCon in 2012. Eric covered it for SemiWiki here. But Synopsys had other stuff they wanted me to blog about and so it is a couple of months late. The 14th month anniversary… Read More

In compliance we trust, for integration we verify

So, you dropped that piece of complex IP you just licensed into an SoC design, and now it is time to fire up the simulator. How do you verify that it actually works in your design? If you didn’t get verification IP (VIP) with the functional IP, it might be a really long day.

Compliance checking something like a PCIe interface block is a … Read More