You are currently viewing SemiWiki as a guest which gives you limited access to the site. To view blog comments and experience other SemiWiki features you must be a registered member. Registration is fast, simple, and absolutely free so please,

join our community today!

Dieter Therssen obtained his master’s degree in Electronics Engineering from KU Leuven in 1987. He started his career as a hardware design engineer, using IMEC’s visionary tools and design methodologies in the early days of silicon integration.

Since then, Dieter developed his career across many digital technologies,… Read More

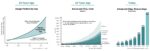

Design Productivity Gap

Twenty-five years ago, SEMATECH first alerted the world to a concern known as the design productivity gap: the observation that the ability to manufacture complex chips had started outpacing the capability of designers to create them by more than a factor of two. This concern was subsequently reiterated… Read More

Dr. Nasib Naser brings over 35 years of experience in the field. His expertise spans the entire VLSI cycle from conception to chip design, with a strong focus on verification methodologies. For his 17 years at Synopsys, Dr. Naser have held senior management positions, leading North American Verification IP, managing Central … Read More

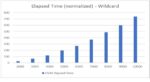

The Universal Verification Methodology (UVM) is a popular way to help verify SystemVerilog designs, and it includes a configuration system that unfortunately has some speed and usage issues. Rich Edelman from Siemens EDA wrote a detailed 20-page paper on the topic of how to avoid these issues, and I’ve gone through it to… Read More

SystemVerilog came to life in 2005 as a superset of Verilog-2005. The last IEEE technical committee revision of the SystemVerilog LRM was completed in 2016 and published as IEEE 1800-2017.

Have the last seven years revealed any changes or enhancements that maintain SystemVerilog’s relevance and efficaciousness in the face … Read More

In today’s fast-paced world, innovation in semiconductor design is a constant demand. The need for quicker, more accurate, and innovative solutions has paved the way for exploring the potential of Generative AI (#GenerativeAI) in the realm of semiconductor design development. Can it be done? Hell yeah! In this article… Read More

In my job, I have the privilege to talk to hundreds of interesting companies in many areas of semiconductor development. One of the most fun things for me is interviewing customers—hands-on users—of specific electronic design (EDA) tools and chip technologies. Cristian Amitroaie, CEO of AMIQ EDA, has been very helpful in introducing… Read More

Almost everything that we do in chip design and verification was invented to raise the abstraction above schematics and polygons. Register-transfer-level (RTL) design, functional simulation, logic synthesis, floorplanning, and more fall into this category. Even the notion of binary circuits is an abstraction. Underneath… Read More

We’re getting close to the annual July Design Automation Conference (DAC) in San Francisco, and every year I like to make the rounds of the exhibitors beforehand and see what’s new. When I checked with AMIQ EDA, I found that this is a big year for them. Their parent company AMIQ just reached its 20th anniversary, and they’ll be celebrating… Read More

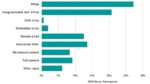

Earlier I blogged about IC and ASIC functional verification, so today it’s time to round that out with the state of FPGA functional verification. The Wilson Research Group has been compiling an FPGA report every two years since 2018, so this marks the third time they’ve focused on this design segment. At $5.8 billion… Read More