You are currently viewing SemiWiki as a guest which gives you limited access to the site. To view blog comments and experience other SemiWiki features you must be a registered member. Registration is fast, simple, and absolutely free so please,

join our community today!

Tell us a little bit about yourself and your company, AMIQ EDA.

We are an EDA company providing software tools targeting both chip design and chip verification. Our tools enable engineers to increase the speed and quality of new code development, simplify debugging and legacy code maintenance, accelerate language and methodology… Read More

You begin writing some UVM code and there are parts of the code that aren’t done yet, so you begin to use uvm_objection, guarding that code. Rich Edelman, a product engineer at Siemens doing verification debug and analysis, wrote a paper on this topic, which I just read. This blog covers the topic of objections and provides some different… Read More

I’ve been working with AMIQ EDA for several years, and have frequently been impressed by new capabilities in their Design and Verification Tools Integrated Development Environment (DVT IDE) family. They just announced AI Assistant, which leverages large language model (LLM) technology. LLMs are much in the news these days,… Read More

Functional coverage acts as a guide to direct verification resources by identifying the tested and untested portions of a design. Functional coverage is a user-defined metric that assesses the extent to which the design specification, as listed by the test plan’s features, has been used. It can be used to estimate the presence… Read More

I stopped by the AMIQ EDA booth at DAC to get an update from Tom Anderson about their Integrated Development Environment (IDE), aimed at helping design and verification engineers save time. In my early IC design days we used either vi or emacs and were happy with having a somewhat smart text editor. With an IDE you get a whole new way … Read More

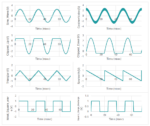

Transistor-level circuit designers have long used SPICE for circuit simulation, mostly because it is silicon accurate and helps them to predict the function, timing, power, waveforms, slopes and delays in a cell before fabrication. RTL designers use digital simulators that have a huge capacity but are lacking analog modeling.… Read More

AMIQ EDA is a pioneer in integrated development environments (IDEs) for hardware design and verification and a provider of platform-independent software tools for efficient code development and analysis. We’ve been attending DAC for many years and are pleased to do so again in 2024. We exhibit at this show for several reasons.… Read More

Agnisys Inc. a leader in design and verification automation for hardware development, is gearing up for an impactful presence at DAC 2024. This year’s participation will be marked by various activities designed to engage and inspire the electronic design automation (EDA) community. Attendees can look forward to our … Read More

This is the first time in 28 years of my visits to DAC that I have seen so many different technologies arrive at DAC in the same year. Earlier we would have one or possibly two innovative breakthroughs in semiconductors and embedded systems that emerged at DAC. This year I expect six or may be seven to arrive, and I am not including the… Read More

Dieter Therssen obtained his master’s degree in Electronics Engineering from KU Leuven in 1987. He started his career as a hardware design engineer, using IMEC’s visionary tools and design methodologies in the early days of silicon integration.

Since then, Dieter developed his career across many digital technologies,… Read More