If you are familiar with Processor IP core, you certainly know DesignWare ARC EM4 core, 32-bit CPU that SoC designers can optimize for a wide range of uses, and differentiate by using patented configuration technology to tailor each ARC core instance to meet specific performance, power and area requirements. If you develop a product… Read More

Tag: synopsys

Server Shift to ARM Becomes a Stampede

I have been at the Linley Microprocessor Conference today. This is the one that is not about mobile: about servers, networking, base-stations. Probably the most important story about the whole industry is that the “shift to ARM becomes a stampede.”

In this market it seems to be driven by the 64-bit ARMv8 instruction… Read More

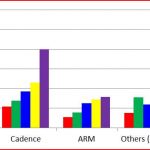

GSA hosting “Interface IP: Winners, Losers in 2013” from IPnest

The GSA IP Working Group will meet today in San Jose, and the Group has asked IPnest building a presentation dedicated to Interface IP. The timing was perfect, as I have just completed the “Interface IP Survey” version 5, and I was able to use fresh market data. The IP working group will discover the IP vendor ranking, protocol by protocol,… Read More

An ASIC Design Flow at LSI

Harish Aepalais part of the Design Closure Methodology group at LSIand he recently talked about his ASIC handoff experience in a webinar. Harish works with logic and physical synthesis, timing constraints, RTL analysis and formal verification.

One challenge with ASIC handoff has been getting through design closure with the… Read More

Can you Publicly Benchmark EDA Tools?

There is an interesting discussion on SemiWiki in regards to the age old question aboutbenchmarking EDA tools. I remember benchmark discussions at my first DAC in 1984. It was deemed impossible to do a “fair” public benchmark then and it’s not possible now, just my opinion of course but let me tell you why. Simply stated it is a legal,… Read More

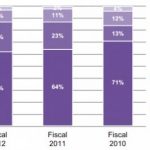

Synopsys: Getting To Know EDA’s Heavyweight Champion

From chip IP vendor ARM Holdings to semiconductor foundry Taiwan Semiconductor, there have been many winners from the mobile device revolution that was sparked by Apple’s introduction of the iPhone. However, while these big-ticket names get all the fame and glory, the electronic design automation space (“EDA” for short) is … Read More

Cadence Grows VIP Business – What’s New?

VIPs (Verification IPs) are really important in this complex world of SoCs which involve various IPs, interfaces and continuously evolving protocols and standards, thus making the task of verifying an overall system extremely challenging. And the verification must be done in minimum possible run-time and memory consumption.… Read More

Stick to the script for repeatable FPGA-based prototyping

70% of today’s ASIC and SoC designs are being prototyped on FPGAs. Everybody knows that. But, did you know that automating the process of converting what could be thousands of ASIC “golden” files into FPGA-friendly versions can mean big savings in a large design?… Read More

Designing Power Management ICs

With all the focus in design on SoCs in the latest sexy process (Hi-K Metal Gate! FinFETs!) it is easy to forget all the other chips that go into a system. When we say “system on a chip” there are actually very few systems that really get everything onto a single chip. One of the big areas that usually cannot go on the latest… Read More

Interface PHY IP supporting Mobile Application on TSMC 20nm? Available!

If we check the many articles daily published in Semiwiki, I am sure that Moore’s Law has been mentioned every single day. There is a good reason why we constantly write about new technologies and advanced features like FinFet, FD-SOI, 450 mm wafers or double patterning: all of these are new challenges that the SC industry will have… Read More