Successful ASIC providers offer top-notch infrastructure and methodologies that can accommodate varied demands from a multitude of customers. Such ASIC providers also need access to best-in-class IP portfolio, advanced packaging and test capabilities, and heterogeneous chiplet integration capability among other things.… Read More

Tag: synopsys

Intel Foundry Services Forms Alliance to Enable National Security, Government Applications

This will be the year of the semiconductor foundry ecosystem, absolutely. Right in between the Samsung SAFE Forum and the TSMC OIP Open Ecosystem Forum, Intel Foundry Services (IFS) just announced a United States Military, Aerospace, and Government (USMAG) Alliance.

Brilliant move, of course, due to the US Government now being… Read More

UCIe Specification Streamlines Multi-Die System Design with Chiplets

Over the last few years, the design of application-specific ICs as well as high-performance CPUs and other complex ICs has hit a proverbial wall. This wall is built from several issues: first, chip sizes have grown so large that they can fill the entire mask reticle and that could limit future growth. Second, the large chip size impacts… Read More

Ansys’ Emergence as a Tier 1 EDA Player— and What That Means for 3D-IC

Over its 40+ year history, electronic design automation (EDA) has seen many companies rise, fall, and merge. In the beginning, in the 1980s, the industry was dominated by what came to be known as the big three — Daisy Systems, Mentor Graphics, and Valid Logic (the infamous “DMV”). The Big 3 has morphed over the years, eventually settling… Read More

Samsung Foundry Forum & SAFE™ Forum 2022

It has been an exciting time in the semiconductor industry and the excitement is far from over. Years 2022 and 2023 will be more challenging in many different ways and live activities have just begun. The cornerstones to the semiconductor industry are the foundries so I look forward to the live foundry events coming up in October,… Read More

WEBINAR: Intel Achieving the Best Verifiable QoR using Formal Equivalence Verification for PPA-Centric Designs

Synopsys Fusion Compiler offers advanced optimizations to achieve the best PPA (power, performance, area) on today’s high-performance cores and interconnect designs. However, advanced transformation techniques available in synthesis such as retiming, multi-bit registers, advanced datapath optimizations, etc. are

An EDA AI Master Class by Synopsys CEO Aart de Geus

I consider Dr. Aart de Geus one of the founding fathers of EDA and one of the most interesting people in the semiconductor industry. So it is not a surprise that Aart was chosen to attend the CHIPs Act signing at the White House.

Here is his current corporate bio:

Since co-founding Synopsys in 1986, Dr. Aart de Geus has expanded Synopsys… Read More

ARC Processor Summit 2022 Your embedded edge starts here!

As embedded systems continue to become more complex and integrate greater functionality, SoC developers are faced with the challenge of developing more powerful, yet more energy-efficient devices. The processors used in these embedded applications must be efficient to deliver high levels of performance within limited power… Read More

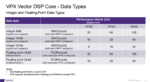

DSP IP for High Performance Sensor Fusion on an Embedded Budget

Whether we realize it or not, everyday applications we use depend on data gathered by sensors. We can bet that pretty much every application uses at least a couple of different types of sensors, if not more. That is because different types of sensors are better suited to collect data depending on the application, the environment … Read More

Memory Security Relies on Ultra High-Performance AES-XTS Encryption/Decryption

A recent SemiWiki post covered the topic of protecting high-speed interfaces in data centers using security IP. That post was based on a presentation made by Dana Neustadter at IP-Soc Silicon Valley 2022 conference. Dana’s talk was an overview of various interfaces and Synopsys’ security IP for protecting those interfaces. … Read More