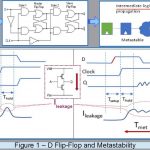

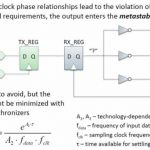

SoC designs frequently have lots of different clock domains to help manage power more efficiently, however one side effect is that when the clock domains meet, i.e., in a Clock Domain Crossing (CDC), there’s the possibility of setup and hold time violations that can cause a flip-flop to become metastable. Synchronizer … Read More

Tag: synchronizer

Clock Domain Crossing in FPGA

Clock Domain Crossing (CDC) is a common occurrence in a multiple clock design. In the FPGA space, the number of interacting asynchronous clock domains has increased dramatically. It is normal to have not hundreds, but over a thousand clock domains interactions. Let’s assess why CDC is a lingering issue, what its impact and the … Read More

Up front phases improve CDC analysis

Many tools find clock domain crossings (CDCs) in FPGA designs. Some don’t find the right ones since they don’t comprehend things like in-house synchronizer constructs. Some find too many based on misunderstanding intent, inaccurate constraints, and other factors that lead to noise.… Read More

Beware of Parameter Variability in Clock Domain Crossings

How should we assess the risk of harmful metastability in a clock domain crossing (CDC) when the semiconductor process has significant parameter variability? One possibility is to determine the MTBF of a synchronizer at the worst-case corner of the CDC. But that approach has some conflicting complications:

- Synchronizer failures

SpyGlass CDC: A Comprehensive solution for addressing CDC issues

About a decade ago, semiconductor designs had just a few asynchronous clocks which were easily managed by designers through the process of manual design reviews. The situation today is completely different. An SoC can have hundreds of asynchronous clocks, driving different complex functions, spread across various IPs, supplied… Read More