Magwel CEO Dündar Dumlugöl is well known from his days at Cadence, where I first met him, and for his more recent tenure at Magwel. At Cadence he led the team that first developed Spectre. He has come a long way from the start of his career at IMEC in Belgium. He and I had a chance to have a conversation recently where he offered insights … Read More

Tag: substrate noise

Will your next SoC fail because of power noise integrity in IP blocks?

By the time that your SoC comes back from the fab and you plugin it into a socket on a board for testing, it’s a little late in the cycle to start thinking about reliability concerns like: dynamic voltage drop, noise coupling, EM (Electro-Migration), self-heating, thermal analysis and ESD (Electro-Static Discharge). They… Read More

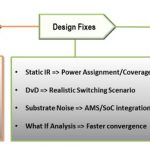

Reliability sign-off has several aspects – One Solution

Here, I am talking about reliability of chip design in the context of electrical effects, not external factors like cosmic rays. So, the electrical factors that could affect reliability of chips could be excessive power dissipation, noise, EM (Electromigration), ESD (Electrostatic Discharge), substrate noise coupling and… Read More

Noise Coupling

One of the challenges of designing a modern SoC is that the digital parts of the circuit are really something that in an ideal world you’d keep as far away from the analog as possible. The digital parts of the circuit generate large amounts of noise, especially in the power supply and in the substrate, two areas where it is impossible… Read More