One of the things that I miss most about attending trade shows like DAC in the old days was that you actually got to see EDA tools being demonstrated live in the exhibit area. You could see what the GUI looked like, how the dialogs worked, and learn what kind of control you could have during analysis. Most of what you see today at DAC in the… Read More

Tag: spice

Drift is a Bad Thing for SPICE Circuit Simulators

My first job out of college was with Intel, located in Aloha, Oregon and I did circuit simulations using a proprietary SPICE circuit simulator called ASPEC that was maintained in-house. While doing some circuit simulations one day I noticed that an internal node in one of my circuits was gradually getting higher and higher, even… Read More

TSMC and Solido to Share Experiences with Managing Variation in Webinar

TSMC knows better than anyone the effect that variation can have at advanced process nodes. Particularly in memory designs and in standard cell designs, variation has become a very critical because of its effects on yield and because of the high-cost of compensating for it. Smaller feature sizes combined with lower voltage thresholds… Read More

Are Your Transistor Models Good Enough?

SoC designers can now capture their design ideas with high-level languages like C and SystemC, then synthesize those abstractions down into RTL code or gates, however in the end the physical IC is implemented using cell libraries made up of transistors. Circuit designers use simulation tools like SPICE on these transistor-level… Read More

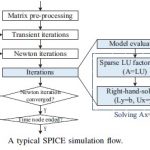

It’s Time to Put Your Spice Netlists on a Diet

Spice circuit simulation remains the backbone of IC design validation. Digital cell library developers rely upon Spice for circuit characterization, to provide the data for Liberty models. Memory IP designers utilize additional Spice features to perform statistical sampling. Analog and I/O interface designers extend these… Read More

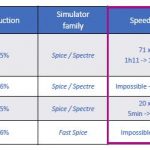

The Emerging Importance of Parallel SPICE

SPICE simulation is the workhorse tool for custom circuit timing validation and electrical analysis. As the complexity of blocks and macros has increased in advanced process nodes — especially with post-layout extraction parasitic elements annotated to the circuit netlist — the model size and simulation throughput… Read More

Process Development, CAD and Circuit Design

Working at Intel as a circuit designer I clearly remember how there were three distinct groups: Process Development, CAD and Circuit Design. Each of the groups sat in a different part of the building in Aloha Oregon, we had different job titles, different degrees, spoke with different acronyms and yet we all had to work together … Read More

Webinar: A Tool for Process and Device Evaluation

Not only are foundries continuing to introduce processes at new advanced nodes, they are frequently updating or adding processes at existing nodes. There are many examples that illustrate this well. TSMC now has 16FF, 16FF+ and now 16FFC. They are also announcing 10nm and 7nm processes. In addition, they are going back to older… Read More

Multi-Level Debugging Made Easy for SoC Development

An SoC can have a collection of multiple blocks and IPs from different sources integrated together along with several other analog and digital components within a native environment. The IPs can be at different levels of abstractions; their RTL descriptions can be in different languages such as Verilog, VHDL, or SystemVerilog.… Read More

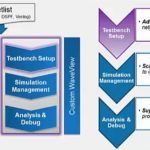

Synopsys’ New Circuit Simulation Environment Improves Productivity — for Free

When technology advances, complexities increase and data size becomes unmanageable. Fresh thinking and a new environment for automation are needed to provide the required increase in productivity. Specifically in case of circuit simulation of advanced-node analog designs, where precision is paramount and a large number… Read More