Over the years SerDes (serializer/deserializer) based connections have proliferated into just about every connection within and among computing systems. Years ago, parallel interfaces were the most common method of moving data, but issues of signal integrity, synchronization and power simply became too much for the required… Read More

Tag: solido

Low Power Design – Art vs. Science

I have heard many times before that low power and mixed-signal design is more Art than Science. I believe this is a misconception. Science is a field that builds upon previous experiences and discoveries. Art primarily seeks out creative differences, things we have not seen before that evoke emotion. The most successful designers… Read More

Mentor FINALLY Acquires Solido Design

I say finally because it was a long time coming… almost ten years to be exact. I started doing business development work for both Solido and Berkeley Design Automation about ten years ago and have been trying to put them together ever since. The synergy was obvious, like peanut butter and jelly. In fact, this is my third time … Read More

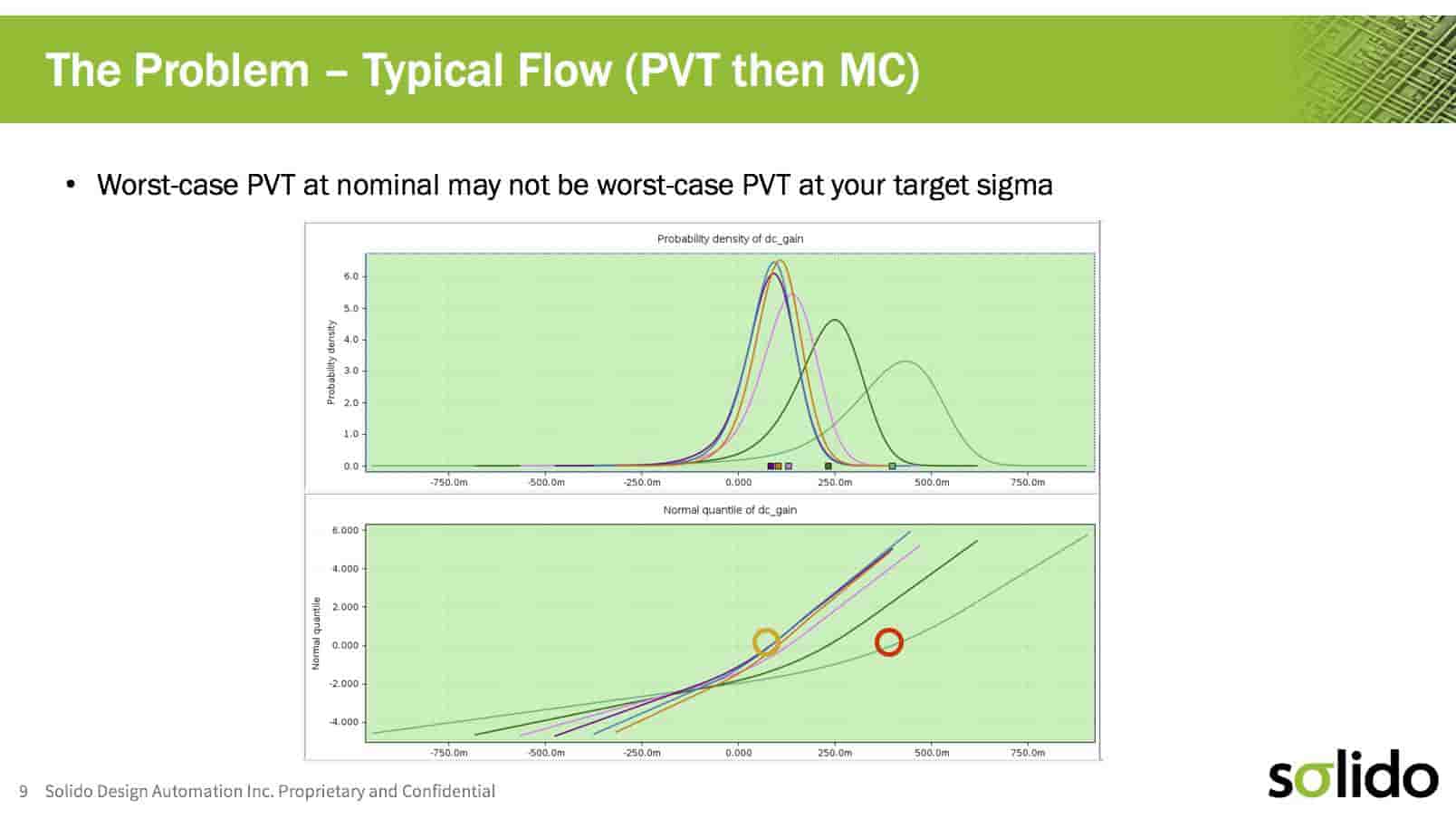

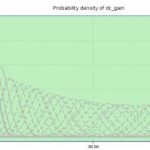

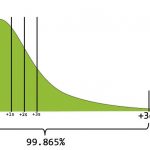

A better way to combine PVT and Monte Carlo to improve yield

TSMC held its Open Innovation Platform Forum the other week on September 13[SUP]th[/SUP]. Each year the companies that exhibit at this event choose to highlight their latest technology. One of the most interesting presentations that I received during the event was from Solido. In recent years they have produced a number of groundbreaking… Read More

Solido Debuts New ML Tool at TSMC OIP!

The TSMC OIP Ecosystem Forum is upon us and what better place to debut a new tool to prevent silicon failures. Solido Design Automation just launched its latest tool – PVTMC Verifier – and will be demonstrating it in their booth at OIP. This is the third product that was developed within its Machine Learning Labs and is… Read More

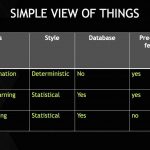

EDA Machine Learning from the Experts!

Traditionally, EDA has been a brute force methodology where we buy more software licenses and more CPUs and keep running endless jobs to keep up with the increasing design and process complexities. SPICE simulation for example; when I meet chip designers (which I do quite frequently) I ask them how many simulations they do for a … Read More

Machine Learning in EDA Flows – Solido DAC Panel

At DAC this year you could learn a lot about hardware design for AI or Machine Learning (ML) applications. We are all familiar with the massively parallel hardware being developed for autonomous vehicles, cloud computing, search engines and the like. This includes, for instance, hardware from Nvidia and others that enable ML … Read More

EDA Powered by Machine Learning panel, 1-on-1 demos, and more!

DAC is upon us again! The Design Automation Conference holds special meaning to me as it was the first technical conference I attended as a semiconductor professional, or professional anything for that matter. That was 33 years ago and I have not missed one since. This year my wife and I both will be walking the DAC floor and it would… Read More

We Need Libraries – Lots of Libraries

It was inevitable that machine learning (ML) would come to EDA. In fact, it has already been here a while in Solido’s variation tools. Now it has found an even more compelling application – library characterization. Just as ML has radically transformed other computational arenas; it looks like it will be extremely disruptive here… Read More

Webinar Offers View into TSMC IP Design Methodology

Standard cell and memory IP are key enablers for new process node availability. These two items must be in place early and be completely ready for a process node to scale to volume. Development of both leaves no room for error and they require the highest performance possible. Foundries are extremely focused on this and spend a lot… Read More