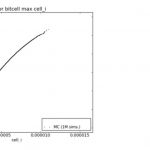

The design of an SRAM array requires focus on the key characteristics of readability, writeability, and read stability. As technology scaling has enabled the integration of large (cache) arrays on die, the sheer number of bitcells has necessitated a verification methodology that focuses on “statistical high-sigma” variation… Read More

Tag: solido design

Solido Has Perfected the Emerging EDA Company Business Model!

Last year at #51DAC we gave away more than a thousand printed versions of our book “Fabless: The Transformation of the Semiconductor industry.” This year we gave away pens with a light and stylus. My friends at Solido Design gave away 600 pens in their booth and we gave away another 400 at our DAC reception on Wednesday night. Solido… Read More

Custom IC Panel: Winning the Custom IC Design Race!

Back in the day, EDA companies enabled the foundries. Seriously, those pesky little foundries chased us EDA companies around like puppies who needed a walk. Now, emerging EDA and IP companies are the puppies and we chase the foundries. Solido Design Automation is one of the hardest working puppies that I have ever helped with strategic… Read More

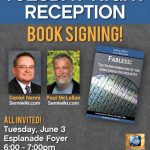

Fabless Book Giveaway at #51DAC!

The generosity of the fabless semiconductor ecosystem never ceases to amaze me. Paul McLellan and I wrote a book for the greater good and now key members of our industry will make sure that 1,500 people at this year’s Design Automation Conference will get copies. As a special thank you to all of our supporters SemiWiki will be hosting… Read More

Variation-Aware Custom IC Design Best Practices

I’ve worked with Solido for 5 years, and it’s been a pleasure to watch the world’s top semiconductor companies and foundries adopt Solido software for their SPICE simulation flows.

Sub-28nm design starts are accelerating, growing from 150 in 2012 to 900 this year. The move to sub-28nm design nodes is being driven by consumer electronic… Read More

Solido Patent Enabling Variation-Aware Custom IC Design

This is patent number twelve for Solido Design Automation THE leading provider of variation analysis and design software for high yield and performance IP and system-on-chip (SOCs). Additional patents are pending on high-sigma analysis, high-dimensional data mining, and other technologies to design and verify custom integrated… Read More

Variation at 28-nm with Solido and GLOBALFOUNDRIES

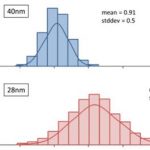

At DAC 2012 GLOBALFOUNDRIES and Solido presented a user track poster titled “Understanding and Designing for Variation in GLOBALFOUNDRIES 28-nm Technology” (as was previously announced here). This post describes the work that we presented.

We set out to better understand the effects of variation on design at 28-nm. In particular,… Read More

High Yield and Performance – How to Assure?

In today’s era, high performance mobile devices are asserting their place in every gizmos we play with and guess what enables them work efficiently behind the scene – it’s large chunks of memory with low power and high speed, packed as dense as possible. Ever growing requirement of power, performance and area led us to process nodes… Read More

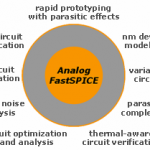

Nanometer Circuit Verification Forum

Verifying circuits on advanced process nodes has always been difficult, and it’s no easier with today’s nanometer CMOS processes. There’s a great paradox in nanometer circuit design and verification. Designers achieve their greatest differentiation when they implement analog, mixed-signal, RF and custom … Read More

Variation-aware Design Survey

Solidohas run an interesting survey on variation-aware design. The data is generic and not specific to Solido’s products although you won’t be surprised to know that they have tools in this area.

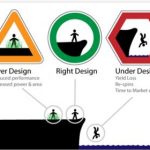

What is variation-aware design? Semiconductor manufacturing is a statistical process and there are two ways to handle this in the design… Read More