One of NetSpeed’s customers is a Tier-1 semiconductor company that develops some of the industry’s best performing and most complex system on chips (SoC) for the data center and cloud computing markets. To keep its leadership in the data center market, the company needs to produce best-in-class SoC solutions year after year. … Read More

Tag: soc

ARM on Moore’s Law at 50: Are we planning for retirement?

On Monday morning on December 7, 2016 Greg Yeric of Arm gave an excellent and wide ranging plenary talk at IEDM entitled “Moore’s Law at 50: Are we planning for retirement?”. You can download Greg’s slide deck here.… Read More

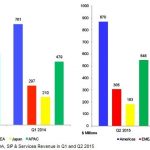

IP Development in Japan

As semiconductor IP is growing bigger in size and more complex in providing complete solution for a particular functionality in an SoC, regions from across the world are joining to provide various types of services in the overall value-chain of IP development, verification, and its integration into SoCs. … Read More

Semiconductors Future Hinges on a Single Pillar

A unique phenomenon has started manifesting itself under the slew of mergers and acquisitions this year in the semiconductor landscape. This phenomenon is bound to intensify in the near future and would positions itself as a key factor for the future of the semiconductor industry. The winners and losers in the game would be determined… Read More

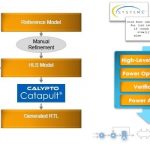

Leveraging HLS/HLV Flow for ASIC Design Productivity

Imagine how semiconductor design sizes leapt higher with automation in digital design, which started from standard hardware languages like Verilog and VHDL; analog design automation is still catching up. However, it was not without a significant effort put in moving designers from entering schematics to writing RTL, which… Read More

Challenges in IP Qualification with Rising Physical Data

With every new technology node, there are newer physical effects that need to be taken into account. And every new physical effect brings with itself several new formats to model them. Often a format is also associated with several of its derivatives, sometimes an standard reincarnation of a proprietary format further evolved… Read More

5 Verification Challenges of IoT Solved by Emulation

Software-centric Emulation environment takes the forefront in modern SoC verification. As more and more devices are IoT enabled, the SoCs have to make special provisions to factor many things including communication, power usage, and network switching, and so on. Also, the demand for an SoC (specifically for smartphone which… Read More

Advances in DDR IP Solution for High-Performance SoCs

In this era of high-performance, low-power, and low-cost devices coming up at an unprecedented scale, the SoCs can never attain the ultimate in performance; always there is scope for improvement. Several methods including innovative technology, multi-processor architecture, memory, data traffic management for low latency,… Read More

HLS with ARM and FPGA Technologies Boosts SoC Performance

The way SoC size and complexity are increasing; new ways of development and verification are also evolving with innovative automated tools and environment for SoC development and optimization. IP based SoC development methodology has proved to be the most efficient for large SoCs. This needs collaboration among multiple players… Read More

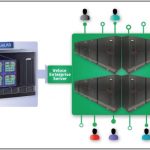

Breaking the Limits of SoC Prototyping

Earlier this month during my conversation with Dr. Walden C. Rhines, he emphasised the need for our next generation designers to think at system level and design everything keeping the system’s view in mind. The verification will go through major transformation at the system level. I can see the FPGA prototyping systems already… Read More