Most SoC designs these days consist largely, but not entirely, of purchased IP blocks. But there are lots of tradeoffs involved in selecting IP blocks, and since those tradeoffs change with process node, even decisions that seem “obvious” based on the last generation of the design, may not be so clear cut. Even if you… Read More

Tag: sip

Moore, or More Than Moore?

Yesterday was the 2013 GSA Silicon Summit, which was largely focused on contrasting what advances in delivering systems will depend on marching down the ladder of process nodes, and which will depend on innovations in packaging technology. So essentially contrasting Moore’s Law with what has come to be known as More Than… Read More

Denali+Tensilica+Cosmic = Cadence

I won’t be able to attend Chris Rowen’s presentation here at the GlobalPress Electronic Summit since I’m going to the first day of the Linley Mobile Microprocessor conference. In fact I wonder if Chris himself will make it since he was running in the Boston marathon on Monday. He finished about 10 minutes before… Read More

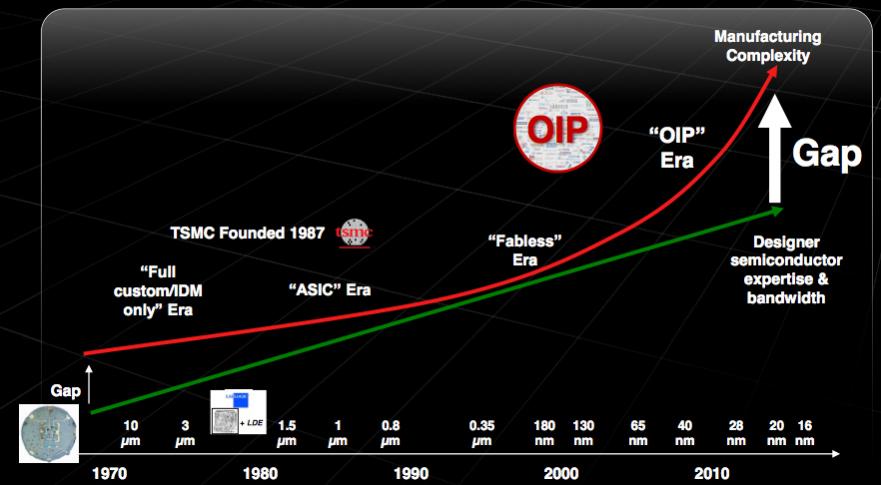

Fabless to OIP

Suk Lee drew the short straw at the TSMC Symposium yesterday, with the 5pm slot. Not only late in the day but between all the attendees and free beer. The morning sessions had been standing room only, with several hundred standees (as they call them on muni around here, but isn’t a standee really someone being stood on?). But … Read More

TSMC ♥ Oasys

Oasys has joined the TSMC Soft-IP Alliance Program. This means that TSMC IP partners have access to a new RTL exploration tool to improve QoR and reduce the iterations needed for design closure. In modern process nodes, RTL engineers implementing complex IP cores for graphics, networking, and mobile computing are struggling … Read More

How We Got Here…

Over at the GSA Forum website I have an article on the history of the semiconductor industry. It is actually based on a couple of brief history of semiconductor blogs (here and here) I published here on SemiWiki last year but edited down a lot and tightened up.

Since the start of the year seems to be the time for predictions, here are the… Read More

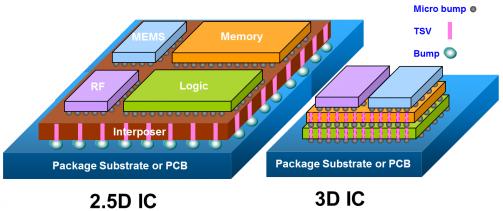

Semiconductor Packaging (3D IC) Emerging As Innovation Enabler!

The ASIC business is getting more and more complicated. The ability to produce innovative die at a competitive price to solve increasingly complex problems just isn’t enough. The technology required to package that die is now front and center.

Here, at the junction of advanced design, process technology and state-of-the art … Read More

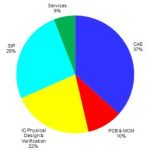

Silicon IP to take over CAE in EDAC results… soon but not yet!

Very interesting results launched by EDAC for Q1 2011, if Computer Aided Engineering (CAE) is still the largest category with $530.6M, the second category is Silicon IP (SIP) with $371.4M, followed by IC Physical Design & Verification at $318.5M. Even more significant is the four quarter moving average results, showing … Read More