We started working with Alphawave at the end of 2020 with a CEO Interview. I had met Tony Pialis before and found him to be a brilliant and charismatic leader so I knew it would be a great collaboration. Tony was already an IP legend after his company was acquired by Intel. After 4+ years at Intel Tony co-founded Alphawave in 2017. Today,… Read More

Tag: Siemens EDA

Averting Hacks of PCIe® Transport using CMA/SPDM and Advanced Cryptographic Techniques

In today’s digital landscape, data security has become an indispensable feature for any data transfer protocol, including Peripheral Component Interconnect Express (PCIe). With the rising frequency and sophistication of digital attacks, ensuring data integrity, confidentiality, and authenticity during PCIe transport… Read More

Electrical Rule Checking in PCB Tools

I’ve known about DRC (Design Rule Checking) for IC design, and the same approach can also be applied to PCB design. The continuous evolution of electronics has led to increasingly intricate PCB designs that require Electrical Rule Checking (ERC) to ensure that performance goals are met. This complexity poses several challenges… Read More

Innexis Product Suite: Driving Shift Left in IC Design and Systems Development

At the heart of the shift-left strategy is the goal of moving traditionally late-stage tasks—such as software development, validation, and optimization—earlier in the design process. This proactive approach allows teams to identify and resolve issues before they escalate, reducing costly rework and shortening the overall… Read More

Prioritize Short Isolation for Faster SoC Verification

Improve productivity by shifting left LVS

In modern semiconductor design, technology nodes continue to shrink and the complexity and size of circuits increase, making layout versus schematic (LVS) verification more challenging. One of the most critical errors designers encounter during LVS runs are shorted nets. Identifying… Read More

SystemVerilog Functional Coverage for Real Datatypes

Functional coverage acts as a guide to direct verification resources by identifying the tested and untested portions of a design. Functional coverage is a user-defined metric that assesses the extent to which the design specification, as listed by the test plan’s features, has been used. It can be used to estimate the presence… Read More

Automating Reset Domain Crossing (RDC) Verification with Advanced Data Analytics

The complexity of System-on-Chip (SoC) designs continues to rise at an accelerated rate, with design complexity doubling approximately every two years. This increasing complexity makes verification a more difficult and time-consuming task for design engineers. Among the key verification challenges is managing reset domain… Read More

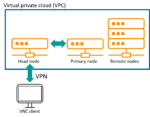

What are Cloud Flight Plans? Cost-effective use of cloud resources for leading-edge semiconductor design

Embracing cloud computing is highly attractive for users of electronic design automation (EDA) tools and flows because of the productivity gains and time to market advantages that it can offer. For Siemens EDA customers engaged in designing large, cutting-edge chips at advanced nanometer scales, running Calibre® design stage… Read More

AI-Powered Transformation in EDA

The integration of artificial intelligence (AI) into Electronic Design Automation (EDA) is revolutionizing chip design, addressing the critical shortage of skilled engineers and accelerating the development process. As Jeff Dyck, Senior Director of Engineering at Siemens EDA, explains in a recent DACtv presentation, … Read More

Solido Siemens and the University of Saskatchewan

In my 40 years, I have worked for dozens of companies and just about everyone of them was acquired. Some of the acquisitions were accretive and some were not. Probably the best and most accretive one would be the Solido acquisition by Siemens EDA in 2017. I worked for Solido for ten years reporting to CEO Amit Gupta. I handled Taiwan … Read More