AMAT reported a more or less in line quarter with revenues of $3.75B and Non-GAAP EPS of $0.81 versus street expectation of $0.79 and revenues of $3.71B. Guidance came in well below the street with revenues expected between $3.33B to $3.63B and Non-GAAP EPS from $0.62 to $0.70 versus expectations of $3.66B and $0.77. The company … Read More

Tag: semiwiki

TSMC and Semiconductors 2019 and Beyond

TSMC has always been my bellwether and for 2019 I think we need to pay careful attention. Bad economic news has been spreading inside the fabless semiconductor ecosystem (tool and IP budgets have been tightening) but I think it is a bit premature. Let’s take a look at the TSMC 2018 Q4 earnings call and talk more about it in the comments… Read More

The New Intel CEO

Interestingly, in some circles I’m known as an “Intel basher” but nothing could be further from the truth. I grew up with Intel and give them full credit for bringing serious compute power to our desktops. My first Intel powered computer was an IBM XT and I have had dozens of Intel based desktops and laptops since then. As a result, I … Read More

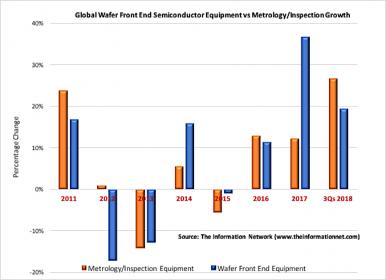

Semiconductor Metrology Inspection Outpacing Overall Equipment Market in 2018

As uncertainties mount about the near-term semiconductor industry from companies in Apple’s supply chain and the significant drop in memory chip prices, the semiconductor industry has consistently grown each year since the great recession of 2009. Semiconductor revenues have consistently outpaced semiconductor equipment… Read More

Intel Discontinues the Custom Foundry Business!

After mentioning what I heard at IEDM 2018, that Intel was officially closing the merchant foundry business as an aside in a SemiWiki forum discussion, I got a lot of email responses so let me clarify. Honestly I did not think it was a big surprise. Intel Custom Foundry was an ill conceived idea (my opinion) from the very start and was… Read More

IEDM 2018 Trip Report!

Hello, my name is Daniel Nenni and I am a semiconductor conference addict. I just can’t seem to get enough. The semiconductor ecosystem is very wide now and moves so quickly it is nearly impossible to keep up without constant conference attendance. As a SemiWiki contributor not only do I get free conference passes, I get access to … Read More

Improving Library Characterization with Machine Learning!

For SOC designers that are waiting for library models the saying “give me liberty or give me death” is especially apropos. Without libraries to support the timing flow, SOC design progress can grind to a halt. As is often the case, more than just a few PVT corners are needed. Years ago, corners were what the term sounded like – the 4 corners… Read More

AMAT and the Jinhua Jinx!

Applied Materials reported a just “in line” quarter but guidance was well below street expectation. AMAT reported EPS of $0.97 and revenues of $4.01B versus street of $0.97 and $4B. Guidance missed the mark by a wide margin with revs of $3.56 to $3.86 and EPS of $0.75 to $0.83 versus already reduced street expectations… Read More

Eliminate PCB Re Spins using an Integrated Multi Dimensional Verification Platform

The rapidly increasing complexity of today’s designs, combined with schedule pressure to deliver innovative products to market as quickly as possible, strains engineering resources to the limit, often to the point of breaking. As a result, 17% of all projects get canceled, and another 28% miss their target release date (Source:… Read More

DAC 2019 to Host the Second System Design Contest!

Interested in showing off your talent in developing deep learning algorithms on embedded hardware platforms for solving real-world problems? Join the second System Design Contest (SDC) at the 56[SUP]th[/SUP] Design Automation Conference in 2019!… Read More