You are currently viewing SemiWiki as a guest which gives you limited access to the site. To view blog comments and experience other SemiWiki features you must be a registered member. Registration is fast, simple, and absolutely free so please,

join our community today!

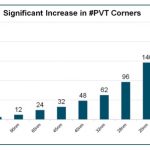

Transistor-level circuit designers have an insatiable appetite to run numerous SPICE circuit simulations in order to determine circuit speed, current and power across Process, Voltage and Temperature (PVT) conditions. Just look at the number of PVT corners increasing as the technology nodes go to 16nm:

The good news today … Read More

There is an interesting discussion on SemiWiki in regards to the age old question aboutbenchmarking EDA tools. I remember benchmark discussions at my first DAC in 1984. It was deemed impossible to do a “fair” public benchmark then and it’s not possible now, just my opinion of course but let me tell you why. Simply stated it is a legal,… Read More

From chip IP vendor ARM Holdings to semiconductor foundry Taiwan Semiconductor, there have been many winners from the mobile device revolution that was sparked by Apple’s introduction of the iPhone. However, while these big-ticket names get all the fame and glory, the electronic design automation space (“EDA” for short) is … Read More

More details are now available for the EDA 50[SUP]th[/SUP] anniversary event on October 16[SUP]th[/SUP]. If you have not been to the museum lately this is a must see event as it is all new. Definitely check out the auction items! Just do not bid against me or it will get very expensive for one of us. I’m watching Storage Wars reruns so… Read More

As a blogger in the EDA industry I get to write every week, however I also end up reading every blog on SemiWiki plus multiple other sites to keep current on what’s happening in our business. I thought that it would be informative to look at Cadence Design Systems and how they are using blogging to talk not just about their own EDA… Read More

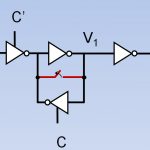

Estimating the MTBF of an SoC should always include an analysis of synchronizer reliability. Contemporary process nodes are introducing new challenges to the reliability of clock domain crossings so it is prudent to revisit how your simulation tool calculates a synchronizer’s MTBF. Let’s list the ten most common pitfalls.… Read More

The power of the fabless semiconductor ecosystem never ceases to amaze me. On one hand you have the Intel backed press crowing about Intel stealing Altera from TSMC. On the other hand you have Xilinx and TSMC crowing about a new ‘one-team’ approach. If you are interested in the real story you’ve come to the right place.

“Altera’s… Read More