When you think Apache Design you probably think Low Power Design and what stuffed animal will they give away at DAC. The other thing you should think about is how the top semiconductor companies around the world use Apache products for leading edge semiconductor design. Demos are fine, but there is nothing like talking directly … Read More

Tag: semiconductors

A Tale of Two Events, Make that Three, Wait…How about Four?

It is increasingly apparent that Kurzweil’s Singularity is sure getting near, if it is not here already 32 years too soon. Not a week goes by without missing or needing to attend a key conference, seminar, symposium, summit, with each having parallel streams, panels, exhibits, demos, social networking. Not only are we informed,… Read More

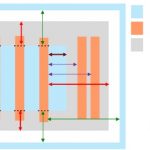

Challenges of 20nm IC Design

Designing at the 20nm node is harder than at 28nm, mostly because of the lithography and process variability challenges that in turn require changes to EDA tools and mask making. The attraction of 20nm design is realizing SoCs with 20 billion transistors. Saleem Haider from Synopsys spoke with me last week to review how Synopsys… Read More

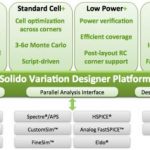

TSMC ♥ Solido

Process variation has been a top trending term since SemiWiki began as a result of the articles, wikis, and white papers posted on the Solido landing page. Last year Solido and TSMC did a webinar together, an article in EETimes, and Solido released a book on the subject. Process variation is a challenge today at 28nm and it gets worse… Read More

Mentor CEO Wally Rhines U2U Keynote

You will never meet a more approachable CEO in the semiconductor ecosystem than Dr. Walden C. Rhines. The first time I met Wally was way back when I blogged for food and he invited me over for lunch. Even better, a year or two later I was having dinner with a friend at the DBL Tree in San Jose. Wally was waiting for his flight home so he joined… Read More

Forte Rises

Over the past few months there has been a bit of back-and-forth concerning the 2012 market data indicating that Forte Designs Systems had taken over the top spot (by revenue) in the high-level synthesis (HLS) market (see stories hereand here). Having worked in this segment for Synfora as VP of Marketing, and as a consultant to AutoESL,… Read More

FinFET Day Presentations at EDPS Monterey!

If you are ever asked to organize a conference session do not hesitate, accept immediately and jump right in. When John Swan, EDPS General Chair, asked me to organize a day I hesitated. Fortunately he is not one to take no for an answer. It was an unforgettable experience on many levels and I hope to be involved with EDPS again next year.… Read More

ISCUG – Excellent Indian Conference, needs to grow

Promoted by Accellera, SystemC User Groups are in work worldwide; NASCUGin North America, ESCUGin Europe and ISCUG in India. While I was shuffling between my day-to-day work and strategy management course/exams, I received an invitation from my long time colleague, President and CEO of Circuitsutra Technologies, Mr. Umesh… Read More

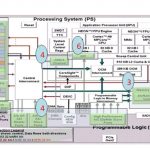

FPGAS – The New Single Board Computers?

I have always felt that FPGAs have been the red haired step child of Silicon Valley. Software weenies have hated them, they are mysterious and take too long to route. Even though they can be massively parallel and the most deterministic piece of silicon you can buy besides a million dollar ASIC, the GPU steals their glory, for now. … Read More

Two New TSMC-Cadence Webinars for Advanced Node Design

Foundries and EDA vendors are cooperating at increasing levels of technical intimacy as we head to the 20nm and lower nodes. Cadence has a strong position in the EDA tools used for IC design and layout of custom and AMS (Analog Mixed-Signal) designs. They have created a series of webinars to highlight the design challenges and new… Read More