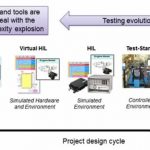

Aerospace and defense applications have traditionally leveraged hardware-in-the-loop (HIL) testing to overcome several issues. A big one is how expensive the physical system is. Even breaking down the system into subsystems for test can still be too expensive when fielding more than a couple test stations. Modeling elements… Read More

Tag: safety critical

NoC resilience protects end-to-end

Protecting memory with ECC but leaving the rest of an SoC uncovered is like having a guard dog chained up in the back corner of your yard. If the problem happens to be in that particular spot, it’ll be dealt with, otherwise there will be a lot of barking but little actual protection.

Similarly, adding a safety-capable processor like… Read More

Cortex-M7: 6-stage, cached, 400 MHz MCU

“Who needs a 32-bit MCU?” It was a question asked a million times in the press when ARM introduced the Cortex-M family back in 2004. In fairness, that question predates the Internet of Things, with wireless sensor networks, open source code, encryption, and more needs for connected devices.… Read More

ISO 26262 driving away from mobile SoCs

Connected cars may be starting to resemble overgrown phones in many ways, but there are critical differences now leading processor teams in a different direction away from the ubiquitous mobile SoC architecture – in turn causing designers to reevaluate interconnect strategies.

The modern car has evolved into a microcontroller… Read More

So, where are all the EMBEDDED guys?

Roaming the aisles at #50DAC the past week left me with one unmistakable impression: there were two shows going on at the same time. Oh, we were all packed into one space together at the Austin Convention Center and neighboring hotels. But we weren’t quite all speaking the same language – yet.… Read More

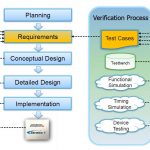

It’s all in the details of FPGA requirements management

Word association: if I said “requirements management”, you’d probably say IBM Rational “DOORS,” or maybe Serena or Polarion if you come from the IT world. But what if the requirements you need to manage are for an FPGA or ASIC, with HDL and testbench code and waveform files and more details backing verification, and compliance… Read More