The rapid evolution of RISC-V processors has introduced unprecedented verification challenges. Modern high-end RISC-V cores now incorporate complex features such as vector and hypervisor extensions, virtual memory systems, multi-level caches, advanced interrupt architectures, and multi-hart out-of-order execution.… Read More

Tag: risc-v

Tiling Support in SiFive’s AI/ML Software Stack for RISC-V Vector-Matrix Extension

At the 2025 RISC-V Summit North America, Min Hsu, Staff Compiler Engineer at SiFive, presented on enhancing tiling support within SiFive’s AI/ML software stack for the RISC-V Vector-Matrix Extension (VME). This extension aims to boost matrix multiplication efficiency, a cornerstone of AI workloads. SiFive’s… Read More

RISC-V Extensions for AI: Enhancing Performance in Machine Learning

In a presentation at the RISC-V Summit North America 2025, John Simpson, Senior Principal Architect at SiFive, delved into the evolving landscape of RISC-V extensions tailored for artificial intelligence and machine learning. RISC-V’s open architecture has fueled its adoption in AI/ML markets by allowing customization… Read More

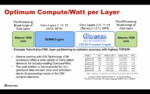

RISC-V: Powering the Era of Intelligent General Computing

Charlie Su, President and CTO of Andes Technology, delivered a compelling keynote at the 2025 RISC-V Summit North America, asserting that RISC-V is primed to drive the burgeoning field of Intelligent General Computing. This emerging paradigm integrates AI and machine learning into everyday computing devices, from AI-enabled… Read More

Journey Back to 1981: David Patterson Recounts the Birth of RISC and Its Legacy in RISC-V

In a warmly received keynote at the RISC-V Summit, computer architecture legend David Patterson took the audience on a captivating trip back to 1981, using scanned versions of his original overhead transparencies to recount the birth of Reduced Instruction Set Computing (RISC) at UC Berkeley.

Patterson began with humor, noting… Read More

Bridging Embedded and Cloud Worlds: AWS Solutions for RISC-V Development

In a compelling keynote at the RISC-V Summit North America 2025, Jeremy Dahan from AWS explored the challenges of embedded systems development and how cloud technologies can bridge the gap between local hardware tinkering and scalable, shareable environments. Drawing from his experience as an engineer, Dahan highlighted … Read More

Navigating SoC Tradeoffs from IP to Ecosystem

Building a complex SoC is a risky endeavor that demands careful planning, strategic decisions, and collaboration across hardware and software domains. As highlighted in Darren Jones’ RISC-V Summit presentation from Andes Technology, titled “From Blueprint to Reality: Navigating SoC Tradeoffs, IP, and Ecosystem,”… Read More

S2C, MachineWare, and Andes Introduce RISC-V Co-Emulation Solution to Accelerate Chip Development

MachineWare, and Andes Technology today announced a collaborative co-emulation solution designed to address the increasing complexity of RISC-V-based chip design. The solution integrates MachineWare’s SIM-V virtual platform, S2C’s Genesis Architect and Prodigy FPGA Prototyping Systems, and Andes’ high-performance… Read More

5 Lessons the Semiconductor Industry Can Learn from Gaming

By Kamal Khan

The semiconductor world has always been the beating heart of tech innovation, powering everything from our smartphones to the latest AI breakthroughs. However, as chip complexity increases and market demands accelerate, adherence to traditional development cycles may be stagnating design teams and slowing … Read More

Demand Meets Design: RISC-V and the Next Wave of AI Hardware

Artificial intelligence (AI) is transforming every layer of computing, from hyperscale data centers training trillion-parameter models to battery-powered edge devices performing real-time inference. Hardware requirements are escalating on every front: compute density is increasing, power budgets are tightening, … Read More