Semiconductor designs have been progressing over time to address wider product varieties and designs with increasing complexity. Organizations have been addressing intense time-to-market pressures by leveraging globally dispersed team resources. The project-centric design methodology, which once worked well with … Read More

Tag: reuse

Water Sustainability in Semiconductor Manufacturing: Challenges and Solutions

Water, the planet’s lifeblood, remains a finite and precious resource. The Earth’s total water supply has remained relatively constant over millennia. However, it is the uneven distribution of freshwater and the challenges of providing access to clean water that are causing stress in various parts of the world.… Read More

UVM Polymorphism is Your Friend

Rich Edelman of Siemens EDA recently released a paper on this topic. I’ve known Rich since our days together back in National Semi. And I’ve always been impressed by his ability to make a complex topic more understandable to us lesser mortals. He tackles a tough one in this paper – a complex concept (polymorphism) in a complex domain… Read More

Scaling Safety Analysis. Reusability for FMEDA

It is common when a new type of analysis is introduced in almost any domain that it works well enough for a while. Until it begins to struggle with growing problem size, prompting refinements to the methodology to allow continued scaling. We see this routinely in analytics for SoC design, so it should not be a big surprise that safety… Read More

Physically Aware SoC Assembly

We used to be comfortable with the idea that the worlds of logical design and physical implementation could be largely separated. Toss the logical design over the wall, and the synthesis and P&R teams would take care of the rest. That idea took a bit of a hit when we realized that synthesis had to become physically aware. The synthesis… Read More

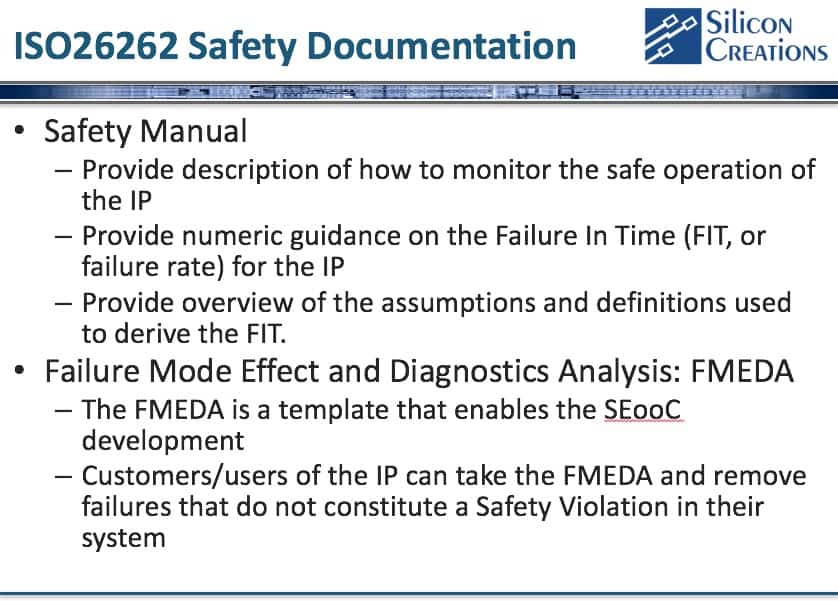

Safety qualification for leading edge IP elements – presentation at REUSE 2017 in Santa Clara

To ensure the reliability of automotive electronics, standards like AEC-Q100 and ISO 26262 have helped tremendously. They have created rational and explicit steps for developing and testing the electronic systems that go into our cars. These are not some abstract future requirement for fully autonomous cars, rather they are… Read More

RTL Correct by Construction

Themes in EDA come in waves and a popular theme from time to time is RTL signoff. That’s a tricky concept; you can’t signoff RTL in the sense of never having to go back and change the RTL. But the intent is still valuable – to get the top-level or subsystem-level RTL as well tested as possible, together with collateral data (SDC, UPF, etc)… Read More

Webinar -New Concepts in Semiconductor IP Lifecycle Management

The semiconductor IP market continues growing at a healthy rate, and IP reuse is a staple of all modern SoC designs. Along with the acceptance of IP reuse comes a host of growing challenges, like:

- Increase in design files

- Increase in meta-data

- More links between design members worldwide

- More links between data in multiple engineering

Aldec Rounds Out ALINT-PRO Checker

If there’s anyone out there who still doesn’t accept the importance of static RTL verification in the arsenal of functional verification methods, I haven’t met any recently. That wasn’t the case in my early days in this field. Back then I grew used to hearing “I don’t make mistakes in my RTL”, “I’ll catch that in simulation”, “My editor… Read More

3 Small-Team Design Productivity Challenges Managed

“Data management tools? We use small teams doing small designs. Each project only has two or three designers. Everyone uses the same EDA tools. Why do we need another tool for collaboration?” Good question. If you enjoy frequent meetings and redoing work because someone didn’t understand the status of IP blocks, the answers may… Read More