Cisco’s relentless push toward higher-performance networking silicon has placed extraordinary demands on its ASIC design methodology. As transistor densities continue to rise across advanced SoCs, traditional design-time guardbands are no longer sufficient to ensure long-term reliability, consistent performance,

Tag: pvt

Silicon Creations Presents Architectures and IP for SoC Clocking

Design & Reuse recently held its IP-SoC Days event at the Hyatt Regency in Santa Clara. Advanced IP is now the fuel for a great deal of innovation in semiconductor design. This popular event allows IP providers to highlight the latest products and services and share a vision of the future. IP consumers can easily get updates on… Read More

The Growing Importance of PVT Monitoring for Silicon Lifecycle Management

In an era defined by complex chip architectures, ever-shrinking technology nodes and very demanding applications, Silicon Lifecycle Management (SLM) has become a foundational strategy for optimizing performance, reliability, and efficiency across the lifespan of a semiconductor device. Central to effective SLM are Process,… Read More

Agile Analog Visit at #60DAC

Chris Morrison, Director of Product Marketing at Agile Analog met with me on the Tuesday at DAC this year, and I asked what has changed in the last year for their analog IP business. The short answer is that the company has initially built up foundation IP for Analog Mixed-Signal (AMS) uses, then recently added new IP for data conversion,… Read More

Automotive IP Certification

The electrification of cars and the growth of EVs means that more semiconductor content is being added with every new vehicle model from suppliers around the globe. There are unique concerns for automotive IP in terms of reliability, security and safety over the lifetime of the vehicle. I had the pleasure to speak with Pawini Mahajan… Read More

Analog Bits and SEMIFIVE is a Really Big Deal

Given the recent acquisitions the ASIC business is coming full circle as a critical part of the fabless semiconductor ecosystem. The most recent one being the SEMIFIVE acquisition of IP industry stalworth Analog Bits. These two companies came to the industry from opposite directions which make them a perfect match, absolutely.… Read More

Webinar: AMS, RF and Digital Full Custom IC Designs need Circuit Sizing

My career started out by designing DRAM circuits at Intel, and we manually sized every transistor in the entire design to get the optimum performance, power and area. Yes, it was time consuming, required lots of SPICE iterations and was a bit error prone. Thank goodness times have changed, and circuit designers can work smarter … Read More

High Reliability Power Management Chip Simulation and Verification for Automotive Electronics

Automotive electronics bring strong demand for power management chips, but its strict reliability requirements also pose new challenges for chip designers. The chip needs to be able to work in various harsh environments such as high temperature, low temperature, aging, abnormal power supply, etc. Although the traditional… Read More

Free Webinar: Analog Verification with Monte Carlo, PVT Corners and Worst-Case Analysis

The letters “PVT” roll of the tongue easily enough, belying the complexity that variations in process, temperature and voltage can cause for analog designs. For semiconductor processes, there are dozens of parameters that can affect the viability of a design. It would be easy enough to optimize a circuit with only one or two varying… Read More

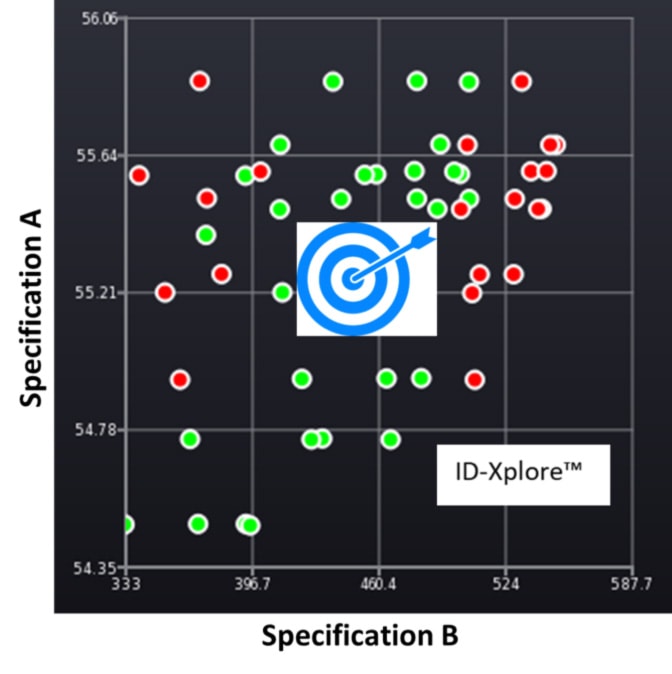

Analog IC design across PVT conditions, something new

Transistor-level design for full-custom and analog circuits has long been a way for IC design companies to get the absolute best performance out of silicon and keep ahead of the competition. One challenge to circuit designers is meeting all of the specs across all Process, Voltage and Temperature (PVT) corners, so that silicon… Read More