You are currently viewing SemiWiki as a guest which gives you limited access to the site. To view blog comments and experience other SemiWiki features you must be a registered member. Registration is fast, simple, and absolutely free so please,

join our community today!

I was at Mentor’s u2u (user group) meeting and one of the keynotes was by Ivo Bolsens of Xilinx. The other was by Wally Rhines and is summarized here.

Ivo started off talking analogizing SoCs as the sports-cars of the industry (fast but expensive), and FPGAs as the station wagons (not cool). In fact he even said that when Xilinx… Read More

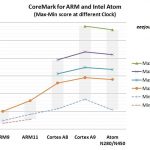

Although there has been always a strong relationship between ARM and GlobalFoundries, it is interesting to notice that Intel has helped to boost it and make it even stronger. Indeed when AMD renegotiated its x86 licensing deal with Intel in 2009, one of the most significant long-term changes was a marked reduction in how much of … Read More

This blog was posted 10 months ago, and the comments have made it much more interesting! Don’t miss the various comments at the back. Also feel free to let us know if you think the status, in this ARM vs Intel “war” has changed a lot since March 2011. Do you really think Intel has catch up with ARM in the mobile industry?… Read More