The letters “PVT” roll of the tongue easily enough, belying the complexity that variations in process, temperature and voltage can cause for analog designs. For semiconductor processes, there are dozens of parameters that can affect the viability of a design. It would be easy enough to optimize a circuit with only one or two varying… Read More

Tag: process variation

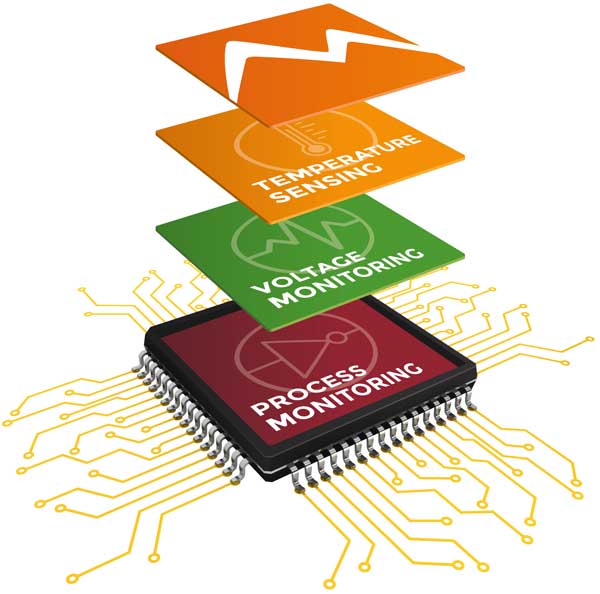

Making AI Silicon Smart with PVT Monitoring

PVT – depending on what field you are in those three letters may mean totally different things. In my undergraduate field of study, chemistry, PVT meant Pressure, Volume & Temperature. Many of you probably remember PV=nRT, the dreaded ideal gas law. However, anybody working in semiconductors knows that PVT stands … Read More

Stop FinFET Design Variation @ #53DAC and get a free book!

If you plan on visiting Solido (the world leader in EDA software for variation-aware design of integrated circuits) at the Design Automation Conference next month for a demonstration of Variation Designer, register online now and get an autographed copy of “Mobile Unleashed”. Such a deal!

Solido Variation Designer is used by… Read More

TSMC and Solido on Variation-Aware Design of Memory and Standard Cell at Advanced Process Nodes

Being that TSMC and Solido are founding members of SemiWiki, you should be able find out everything you ever wanted to know on their respective landing pages. If not, just ask a question in the SemiWiki forum and I can assure you it will be answered in great detail. And here are some other interesting 2015 factoids from Solido:… Read More

A Better Way for Analog Designers to Perform Variation Analysis

The impact of process variation at advanced nodes is increasing — no surprise there. In recent years, the principal design emphasis to better reflect this variation has been the adoption of two new methodologies: (1) advanced on-chip variation (AOCV, as well as POCV/LVF) for digital static timing analysis, and (2) advanced… Read More

Improvements in SRAM Yield Variation Analysis

The design of an SRAM array requires focus on the key characteristics of readability, writeability, and read stability. As technology scaling has enabled the integration of large (cache) arrays on die, the sheer number of bitcells has necessitated a verification methodology that focuses on “statistical high-sigma” variation… Read More

Custom IC Panel: Winning the Custom IC Design Race!

Back in the day, EDA companies enabled the foundries. Seriously, those pesky little foundries chased us EDA companies around like puppies who needed a walk. Now, emerging EDA and IP companies are the puppies and we chase the foundries. Solido Design Automation is one of the hardest working puppies that I have ever helped with strategic… Read More

SEMulator3D: GlobalFoundries Process Variation Reduction

At SEMICON last month, Rohit Pal of GlobalFoundries gave a presentation on their methodology for reducing process variation. It was titled Cpk Based Variation Reduction: 14nm FinFET Technology.

Capability indices such as Cpk is a commonly used technique to assess the variation maturity of a technology. It looks at a given parameter’s… Read More

Variation-Aware Custom IC Design Best Practices

I’ve worked with Solido for 5 years, and it’s been a pleasure to watch the world’s top semiconductor companies and foundries adopt Solido software for their SPICE simulation flows.

Sub-28nm design starts are accelerating, growing from 150 in 2012 to 900 this year. The move to sub-28nm design nodes is being driven by consumer electronic… Read More

What Can Accelerate 3D Semiconductor Manufacturing?

In the beginning of this decade there was a lot of buzz around 3D chip manufacturing. Many EDA tools were developed to facilitate semiconductor designs in 3D space. Naturally, we are moving to the edge on 2D without much room to further squeeze transistors and interconnect. However, lately I haven’t heard much about 3D products.… Read More