You are currently viewing SemiWiki as a guest which gives you limited access to the site. To view blog comments and experience other SemiWiki features you must be a registered member. Registration is fast, simple, and absolutely free so please,

join our community today!

At 3nm and below, clock networks have quietly become the dominant limiter of SoC power, performance, and yield. Yet most advanced-node designs still rely on abstraction-based signoff methodologies developed when voltage headroom was generous and interconnect effects were secondary.

That assumption no longer holds

As supply… Read More

Often, AI inference brings to mind more complex applications hungry for more processing power. At the other end of the spectrum, applications like home appliances and doorbell cameras can offer limited AI-enabled features but must be narrowly scoped to keep costs to a minimum. New area-optimized AI inference technology from… Read More

The latest advanced driver-assistance systems (ADAS) like Mercedes’ Drive Pilot and Tesla’s FSD perform SAE Level 3 self-driving, with the driver ready to take back control if the vehicle calls for it. Reaching Level 5 – full, unconditional autonomy – means facing a new class of challenges unsolvable with existing technology… Read More

Artificial intelligence (AI) and machine learning (ML) are hot topics. Beyond the impact these technologies are having on the world around us, they are also having impact on the semiconductor and EDA ecosystem. I posted a blog last week that discussed how Cadence views AI/ML, both from a tool and ecosystem perspective. The is one… Read More

At DesignCon 2020, ANSYS held a series of sponsored presentations. I was able to attend a couple of them. These were excellent events with the material delivered by talented and high-energy speakers. The DesignCon technical program has many dimensions beyond the conference tracks. One of the presentations dealt with 3D ICs.… Read More

In a joint presentation given by Samsung, Arm, and Cadence at the Arm TechCon event on October 9, 2019, Cadence showed some results and explained its collaboration project used to implement the new Arm Hercules CPU on Samsung’s advanced 5LPE process. I do not want to minimize the significance of Samsung’s and Arm’s participation… Read More

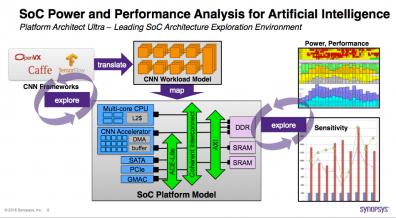

Discussion on machine learning (ML) and hardware design has been picking up significantly in two fascinating areas: how ML can advance hardware design methods and how hardware design methods can advance building ML systems. Here I’ll talk about the latter, particularly about architecting ML-enabled SoCs. This approach is … Read More