Physical AI is changing how intelligent systems interact with the real world. These systems must sense, process, and respond to data in real time. Unlike cloud AI, Physical AI depends on fast local processing and reliable distributed communication. This shift creates a new challenge. Systems must move large volumes of sensor… Read More

Tag: pcie 5.0

Why Choose PCIe 5.0 for Power, Performance and Bandwidth at the Edge?

Synopsys recently held a webinar session on this topic and Gustavo Pimentel, Principal Product Marketing Manager at the company led the webinar session. Going into the webinar session, I found myself wondering: why focus on PCIe 5.0, eight years after its release? With the industry buzzing about Edge AI, cloud computing, and … Read More

Mitigating AI Data Bottlenecks with PCIe 7.0

During a recent LinkedIn webcast, Dr. Ian Cutress, Chief Analyst at More than Moore and Host at TechTechPotato, and Priyank Shukla, Principal Product Manager at Synopsys, shared their thoughts regarding the industry drivers, design considerations, and critical advancements in compute interconnects enabling data center… Read More

PCIe 6.0, LPDDR5, HBM2E and HBM3 Speed Adapters to FPGA Prototyping Solutions

We live in the age of big data. No matter how fast and complex modern SoCs are, it all comes down to how quickly data can get in and out that determines the system performance. And, there is a lot of data that today’s systems need to process. Naturally, system interfaces such as PCIe, DDR, HBM, etc., have been evolving rapidly too, to support… Read More

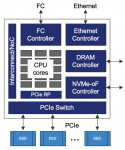

PLDA Brings Flexible Support for Compute Express Link (CXL) to SoC and FPGA Designers

A few months ago, I posted a piece about PLDA expanding its support for two emerging protocol standards: CXL™ and Gen-Z™. The Compute Express Link (CXL) specification defines a set of three protocols that run on top of the PCIe PHY layer. The current revision of the CXL (2.0) specification runs with the PCIe 5.0 PHY layer at a maximum… Read More

Analog Bits at TSMC OIP – A Complete On-Die Clock Subsystem for PCIe Gen 5

This is another installment covering TSMC’s very popular Open Innovation Platform event (OIP), held on August 25. This event presents a diverse and high-impact series of presentations describing how TSMC’s vast ecosystem collaborates with each other and with TSMC. The talk covered here focuses on a complete on-die clock … Read More

PLDA – Delivering Quality IP with a Solid Verification Process and an Extensive Ecosystem

For those who design advanced and complex SoCs, the term “off-the-shelf IP” can be elusive. While this approach works for a wide range of IP titles, the pressure for maximum performance or minimum power can lead to custom-tailoring requirements for the IP.

PLDA has seen these requirements for the class of complex, high-performance… Read More

Turbo-Charge Your Next PCIe SoC with PLDA Switch IP

SemiWiki has a new IP partner, PLDA and they bring a lot to the party. Peripheral component interconnect express (PCIe) is a popular high-performance data interface standard. Think GPUs, RAID cards, WiFi cards or solid-state disk (SSD) drives connected to a motherboard. The protocol offers much higher throughput than previous… Read More

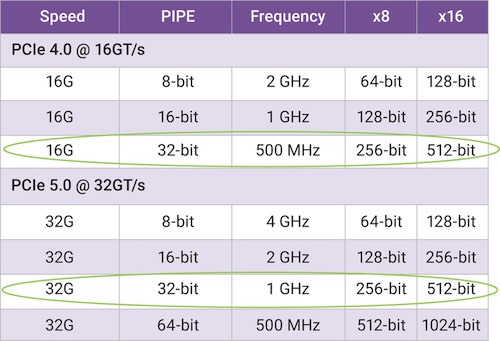

PCIe 5.0 Jumps to the Fore in 2019

2019 will be a big year for PCIe. With the approval of version 0.9 of the Base Layer for PCIe 5.0, implementers have a solid foundation to begin working on designs. PCIe 4.0 was introduced in 2017, before that the previous PCIe 3.0 was introduced in 2010 – ages ago in this industry. In fact, 5.0 is so close on the heels of 4.0, many products… Read More