Here, I am talking about reliability of chip design in the context of electrical effects, not external factors like cosmic rays. So, the electrical factors that could affect reliability of chips could be excessive power dissipation, noise, EM (Electromigration), ESD (Electrostatic Discharge), substrate noise coupling and… Read More

Tag: pathfinder

Power and Reliability Sign-off – A must, but how?

At the onset of SoCs with multiple functionalities being packed together at the helm of technologies to improve upon performance and area; power, which was earlier neglected, has become critical and needs special attention in designing SoCs. And there comes reliability considerations as well due to multiple electrical and … Read More

ESD Check Methodology

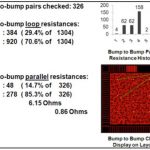

In Pune at the start of the month, Norman Chang, Ting-Sheng Ku, Jai Pollayil of Apache/Ansys and NVIDIA presented and ESD check methodologywith Fast Full-chip Static and Macro-level Dynamic Solutions . ESD stands for Elecro-Static Discharge and is basically injecting very high static voltages (think how your hand gets charged… Read More

PathFinder webinar: Full-chip ESD Integrity and Macro-level Dynamic ESD

The PathFinder webinar will be at 11am Pacific time on Thursday 4th August. It will be conducted by Karthik Srinivasan, Senior Applications Engineer at Apache Design Solutions. Mr. Srinivasan has over four years of experience in the EDA industry, focusing on die, system, and cross-domain analysis. His professional interests… Read More

Analyzing and Planning Electro-static Discharge (ESD) Protection

ESD has historically been a big problem analyzed with ad-hoc approaches. As explained earlier, this is no longer an adequate way to plan nor signoff ESD protection.

Pathfinder is the first full-chip comprehensive ESD planning and verification solution. It is targeted to address limitations in today’s methodologies.… Read More

Electro-static Discharge (ESD)

Electro-static discharge (ESD) has been a problem since the beginning of IC production. Chips function on power supplies of up to a few volts (depending on the era) whereas ESD voltages are measured in the thousands of volts. When you reach out for your car door handle and a spark jumps across, that is ESD. If you were touching a chip… Read More