After teams sweat the details of SoC and industrial design, they turn to printed circuit board designers for magic. Here are a pile of chips and passives, and a schematic for interconnecting them. This is how much physical space the board can occupy. Connectors have to be here, and here, and mounting holes there, and there. There … Read More

Tag: optimization

WLAN Design Optimization at Lantiq

Right now I’m typing on my MacBook Pro computer connected to the Internet through WiFi, thanks to the electronics in both my laptop and WiFi router. I kind of take WiFi for granted because it is so ubiquitous throughout my daily life, yet there are IC designers at companies like Lantiq Semiconductorthat have to design and optimize… Read More

Transistor-level Sizing Optimization

RTL designers know that their code gets transformed into gates and cells by using a logic synthesis tool, however these gates and cells are further comprised of transistors and sometimes you really need to optimize the transistor sizing to reach power, performance and area goals. I’ve done transistor-level IC design before,… Read More

How to Reduce Maximum Power at RTL Stage?

Of course that reduction has to stay throughout the design cycle up to layout implementation and fabrication. Since the advent of high density, mega functionality SoC designs at advanced nodes and battery life critical devices played by our fingertips, the gap between SoC power requirement and actual SoC power has only increased.… Read More

Key Ingredients for ESL Power Modeling, Simulation, Analysis and Optimzations

There’s a French EDA company named DOCEA Powerthat is uniquely focused on power analysis at the ESL level and I had a chance to interview Ridha Hamza to get new insight on ESL design challenges and their approach. Ridha started out doing SRAM design at STMicroelectornics in the 1990’s, moved into the emerging field … Read More

Untangling snags earlier and reducing area by 10%

The over 20 years of experience behind Synopsys Design Compiler is getting a new look for 2014, and we had a few minutes with Priti Vijayvargiya, director of product marketing for RTL synthesis, to explore what’s in the latest version of the synthesis tool.

Previewed today, Synopsys Design Compiler 2013.12 continues to target … Read More

High-Sigma Standard Cell Optimization!

Standard cell optimization is an important problem, because the speed, power, and area of cells has a direct impact speed, power, and area of the whole chip. Typically, standard cell optimization been done with simple in-house local-optimizer scripts. However, these optimizers have had several flaws: they don’t properly capture… Read More

What’s in your network processor?

Recently, one of those very restrained press releases – in this case, Mentor Graphics and Imagination Technologiesextending their partnership for MIPS software support– crossed my desk with about 10% of the story. The 90% of this story I want to focus on is why Mentor is putting energy into this partnership… Read More

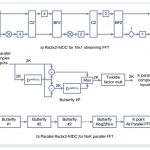

Gigahertz FFT rates on a 500MHz budget

A basic building block of any communication system today is the fast Fourier transform, or FFT. A big advantage of FPGA implementations of FFTs is they can be scaled and tuned for the task at hand, optimizing data flow, resource use, and power consumption. Scaled, that is, up to the clock speed of the FPGA – or so it would seem.

Today’s… Read More

When the lines on the roadmap get closer together

Tech aficionados love roadmaps. The confidence a roadmap instills – whether using tangible evidence or just a good story – can be priceless. Decisions on “the next big thing”, sometimes years and a lot of uncertain advancements away, hinge on the ability of a technology marketing team to define and communicate a roadmap.

Any roadmap… Read More