Performance, Power and Area (PPA) metrics are the driving force in the semiconductor market and impact all electronic products that are developed. PPA tradeoff decisions are not engineering decisions, but rather business decisions made by product companies as they decide to enter target end markets. As such, the sooner a company… Read More

Tag: N5

Application-Specific Lithography: 5nm Node Gate Patterning

It has recently been revealed that the N5 node from TSMC has a minimum gate pitch of 51 nm [1,2] with a channel length as small as 6 nm [2]. Such a tight channel length entails tight CD control in the patterning process, well under 0.5 nm. What are the possible lithography scenarios?

Blur Limitations for EUV Exposure

A state-of-the-art

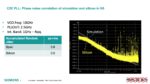

On-Chip Sensors Discussed at TSMC OIP

TSMC recently held their Open Innovation Platform (OIP) Ecosystem Forum event where many of their key partners presented on their latest projects and developments. This year one of their top IP provider partners, Analog Bits, gave two presentations. Analog building blocks have always been necessary as enabling technology … Read More

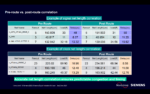

In-Chip Monitoring Helps Manage Data Center Power

Designers spend plenty of time analyzing the effects of process, voltage and temperature. But everyone knows it’s not enough to simply stop there. Operating environments are tough and have lots of limitations, especially when it comes to power consumption and thermal issues. Thermal protection and even over-voltage protections… Read More