The impact of process variation at advanced nodes is increasing — no surprise there. In recent years, the principal design emphasis to better reflect this variation has been the adoption of two new methodologies: (1) advanced on-chip variation (AOCV, as well as POCV/LVF) for digital static timing analysis, and (2) advanced… Read More

Tag: monte carlo

Path FX – the Production Proven Answer to Static Timing Analysis with Variation

I want to compliment ChipGuy on a very nice write-up of a complex topic – how to model process variation in static timing.

… Read More

Synopsys’ New Circuit Simulation Environment Improves Productivity — for Free

When technology advances, complexities increase and data size becomes unmanageable. Fresh thinking and a new environment for automation are needed to provide the required increase in productivity. Specifically in case of circuit simulation of advanced-node analog designs, where precision is paramount and a large number… Read More

Moving with Purpose for Certainty

In 1492 Christopher Columbus sailed from Spain towards west on Atlantic Ocean in search of Asia and Indies. Between his four voyages (1492 – 1502) he discovered many different islands and then what we call Americas. Although he had a compass with him, imagine searching a needle in a haystack. Even with localization of areas and then… Read More

Replacing the British Museum Algorithm

In principle, one way to address variation is to do simulations at lots of PVT corners. In practice, most of this simulation is wasted since it adds no new information, and even so, important corners will get missed. This is what Sifuei Ku of Microsemi calls the British Museum Algorithm. You walk everywhere. And if you don’t walk to… Read More

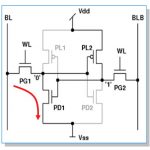

Optimizing SRAM IP for Yield and Reliability

My IC design career started out with DRAM at Intel, and included SRAM embedded in GPUs, so I recall some common questions that face memory IP designers even today, like:

- Does reading a bit flip the stored data?

- Can I write both 0 and 1 into every cell?

- Will read access times be met?

- While lowering the supply voltage does the cell data retain?

Designing for Variation

There is a widespread phenomenon in designing chips that new effects creep up on you. First they are so small you can ignore them. Then you can add a little pessimism to your timing budget or whatever gets affected. But eventually the effects go from second order to first order. You certainly can’t ignore them, and the guard … Read More

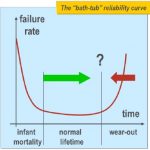

Predicting Lifetime of Analog ICs

With the increase of transistors per unit area, high density interconnects and manufacturing variability at lower nodes, the electronic devices have become more vulnerable to failures. The devices that operate under extreme conditions such as automotive devices that operate at high temperatures need to be robust enough to… Read More

IC Variability Analysis at DAC

There were a handful of EDA vendors at DAC this year touting tools for IC variability analysis. On Tuesday I met with Firas Mohamed, CEO and President of Infiniscale.… Read More

Fast Monte Carlo from Infiniscale at DAC

Firas Mohamed, President and CEO (Ph.D.) of Infiniscale met with me on Monday at DAC to provide an overview of what EDA software they offer to IC designers at the transistor-level.

Vision – analog flow that Monte Carlo simulation is required, which is thousands of circuit simulations, however the higher the sigma the more… Read More