You are currently viewing SemiWiki as a guest which gives you limited access to the site. To view blog comments and experience other SemiWiki features you must be a registered member. Registration is fast, simple, and absolutely free so please,

join our community today!

SMACD 2026by Admin on 01-07-2026 at 3:03 am

Welcome to SMACD 2026

International Conference on Synthesis, Modeling, Analysis and Simulation Methods, and Applications to Circuit Design

REGISTER HERE… Read More

From my vantage point in the EDA foxhole it can be easy to forget that Cadence also has interests in much broader technology domains. One of these is in data center modeling and optimization, through their Cadence Reality Digital Twin Platform. This is an area in which they already have significant track record collaborating with… Read More

AI and machine learning are two popular buzz words in the high-tech daily news, so you should be getting used to hearing about them by now. What I hadn’t realized was that EDA companies are starting to use machine learning techniques, and specifically targeted at the daunting and compute intensive task of creating SPICE models… Read More

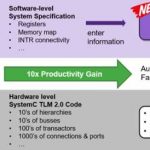

Virtual prototyping has, inexplicably, been largely a DIY thing so far. Tools and models have come from different sources with different approaches, and it has been up to the software development team to do the integration step and cobble together a toolchain and methodology that fits with their development effort.

That integration… Read More

Watching a spirited debate on Twitter this morning between Tom Peters and some of his followers reminded me of the plot of many spy movies: silently killing an opponent with a lethal injection of some exotic, undetectable poison. We are building in enormous risks in more and more big data systems.… Read More

As I sat down in the SEMI Arizona Chapter breakfast meeting a few weeks ago, a moment of semiconductor history flew right before my eyes before the IoT sessions started.

We were seated in the cafeteria of Freescale Building 94 on Elliot Road in Tempe, a place I’d been many times before, except this time may have been the last. NXP is consolidating… Read More

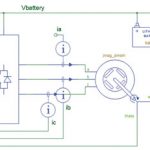

With electronic and software content in vehicles skyrocketing, and the expectations for flawless operation getting larger, the need for system-level verification continues to grow. Last month, we looked at a Synopsys methodology for virtual hardware in the loop, or vHIL… Read More

We’re putting the finishing touches on Chapter 9 of our upcoming book on ARM processors in mobile, this chapter looking at the evolution of Qualcomm. One of the things that made Qualcomm go was their innovative use of digital simulation. First, simulation proved out the Viterbi decoder (which Viterbi wasn’t convinced had a lot … Read More

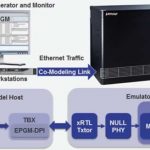

Ethernet is suddenly a hot topic in SoC design again. The biggest news may be this: it’s not just the cloud and enterprise networks. Those are still important applications. The cloud is driving hard for more ports at 25G server and 100G switch speeds according to a recent Dell’Oro Group report. Enterprise networks are driving for… Read More

In optimizing SoC design for performance, there is so much focus on how fast a CPU core is, or a GPU core, or peripherals, or even the efficiency of the chip-level interconnect. Most designers also understand selecting high performance memory at a cost sweet spot, and optimizing physical layout to clock it as fast as possible within… Read More