Test experts use the acronym BIST for Built In Self Test, it’s the test logic added to an IP block that speeds up the task of testing by creating stimulus and then looking at the output results. Memory IP is a popular category for SoC designers, as modern chips include multiple memory blocks for fast, local data and register storage… Read More

Tag: mbist

MBIST Power Creates Lurking Danger for SOCs

The old phrase that the cure is worse than the disease is apropos when discussing MBIST for large SOCs where running many MBIST tests in parallel can exceed power distribution network (PDN) capabilities. Memory Built-In Self-Test (MBIST) usually runs automatically during power on events. Due to the desire to speed up test and … Read More

Novel DFT Approach for Automotive Vision SoCs

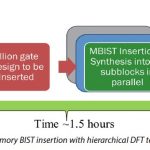

You may have seen a recent announcement from Mentor, a Siemens business, regarding the use of their Tessent DFT software by Ambarella for automotive applications. The announcement is a good example of how Mentor works with their customers to assure design success. On the surface the announcement comes across as a nice block and… Read More

DFT Innovations Come from Customer Partnerships

There is an adage that says that quality is not something that can be slapped on at the end of the design or manufacturing process. Ensuring quality requires careful thought throughout development and production. Arguably this adage is more applicable to the topic of Design for Test (DFT) than almost any other area of IC development… Read More

Can a hierarchical Test flow be used on a flat design?

It is pretty common for physical layout to work from a flattened hierarchy for blocks or even full chips, even though the front-end design starts with a hierarchical representation. This was not always the case. Way back when, the physical layout matched the logical hierarchy during the design process. Of course, this led to all… Read More

Automotive Market Pushing Test Tool Capabilities

It’s easy to imagine that the main impetus for automotive electronics safety standards like ISO 26262 is the emergence of autonomous driving technology. However, even cars that do not offer this capability rely heavily on electronics for many critical systems. These include engine control, braking, crash sensors, and stability… Read More

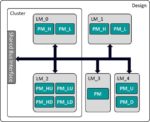

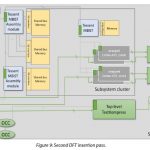

Hierarchical RTL Based ATPG for an ARM A75 Based SOC

Two central concepts have led to the growth of our ability to manage and implement larger and larger designs: hierarchy and higher levels of abstraction. Without these two approaches the enormous designs we are seeing in SOCs would not be possible. Hierarchy in particular allows the reuse of component blocks, such as CPU cores.… Read More

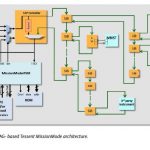

Auto Introspection

It is an indictment of our irrationality that our cars are now more health-conscious than we are. Increasingly safety-conscious readings of the ISO26262 standard now encourage that safety-critical electronics (anti-lock braking control for example) automatically self-test, not just at power-on but repeatedly as the car… Read More

Physically Aware DFT Improves PPA

Introducing on-chip test circuitry has become a necessary criteria for an ASIC’s post manufacture testability. The test circuitry is usually referred as DFT (Design-for-Test) circuit. A typical methodology for introducing DFT circuit in a design is to replace usual flip-flops with special types of flip-flops called ‘scan… Read More

Improve Test Robustness & Coverage Early in Design

In a semiconductor design, keeping the design testable with high test coverage has always been a requirement. However with shrinking technology nodes and large, dense SoC designs and complex logic structures, while it has become mandatory to reach close to 100% test coverage, it’s extremely difficult to cope with the explosion… Read More