You are currently viewing SemiWiki as a guest which gives you limited access to the site. To view blog comments and experience other SemiWiki features you must be a registered member. Registration is fast, simple, and absolutely free so please,

join our community today!

There was a “research reviewed” panel on Thursday at DAC entitled Shortening the Wires Between High-Level Synthesis and Logic Synthesis. Chaired by Alric Althoff of Tortuga Logic, the panel explored methods to deal with wire delays in high-level synthesis and logic synthesis. The four speakers and their focus were:

…

Read More

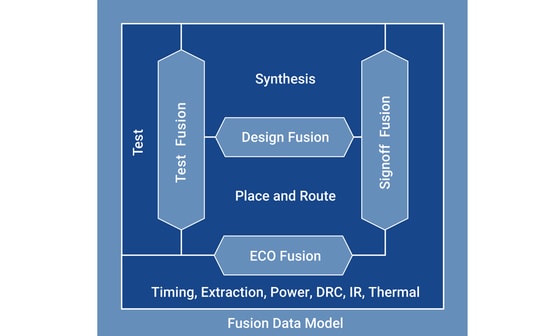

There were many interesting presentations at ARM TechCon this year besides the keynote addresses by Arm, which were truly stunning for content and production value. One very interesting presentation was the talk given in the afternoon of Wednesday, October 9, 2019, titled, Synopsys Fusion Compiler for Next Generation Arm Hercules… Read More

Synopsys is pretty well-known for their early entry into logic synthesis with the Design Compiler tool and more recent P&R tool with IC Compiler, so I met up with two folks at DAC to get a better idea of what this new Fusion technology was all about where the barriers between tools are changing. Michael Jackson and Rahul Deokar … Read More

I remember meeting Ken McElvain at Silicon Compilers for the first time back in the 1980’s, he was a gifted EDA tool developer that did a lot of coding including logic synthesis, a cycle-based simulator and ATPG. Mentor Graphics acquired Silicon Compilers with Ken included, and he continued to create another logic synthesis… Read More

Back in the microprocessor stone age, government procurement agencies fell in love with the idea of radiation hardened parts that might survive catastrophic events. In those days, before rad-hard versions of PowerPC and SPARC arrived, there were few choices for processors in defense and space programs.

One of the first rad-hard… Read More

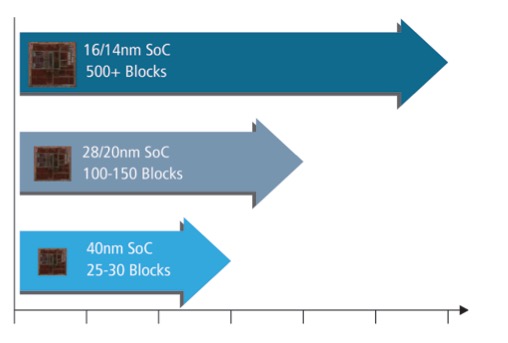

Combine the pressures of Moore’s Law which enable billion transistor SoCs and the shortened time to market from consumer electronics product cycles and you have the perfect storm for EDA tool vendors. A modern SoC can have 500 or more blocks, creating both a design and verification challenge. How in the world do you write … Read More

Previously, I examined chip design in the late 1970s and early 1980s. It was a nostalgic ride – thanks to all those who shared their stories. I enjoyed reading all of them. I drew two basic conclusions in the prior post:

[LIST=1]

Chip design problems are the same, more or less, over time. The numbers just get bigger

Raising abstraction…

Read More

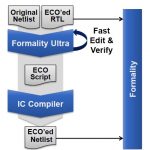

Your latest SoC has just begun the tape-out process and then marketing comes back with a small update to the specification to make your design more competitive, or maybe your regression tests just found a minor bug in a single IP block that needs to be fixed. Should you go back in your design flow, change the RTL source code and then completely… Read More

Synopsys was started in 1986 and so 2011 was its 25th anniversary. They created a little timeline with some of their history. As with most companies, the earlier history is the most interesting, before it was clear what the future would bring. From 1986 to 1990 they grew to $22M in revenue, which was explosive growth. So explosive … Read More