IC design challenges are different at advanced nodes like 7nm, so to learn more about the topic I attended a panel luncheon at DAC sponsored by Cadence. The moderator was both funny and technically astute, quite the rare combination, so kudos to Professor Rob Rutenbar, a former Neolinear guy now at the University of Illinois. Panelists… Read More

Tag: ic design

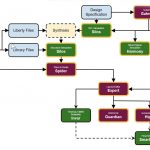

Custom IC Design Flow with OpenAccess

Imagine being able to use any combination of EDA vendor tools for schematic capture, SPICE circuit simulation, layout editing, place & route, DRC, LVS and extraction. On the foundry side, how about creating just a single Process Development Kit (PDK), instead of vendor-specific kits. Well, this is the basic premise of a recent… Read More

IC Design and OpenAccess

EDA vendors have long used proprietary file and database formats to keep their users locked into their specific tool flow and keep any competitors from sharing in the IC design process. Along the way the actual users of EDA tools have often requested and helped to create interoperable flows so that they could mix and match multiple… Read More

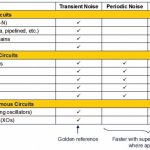

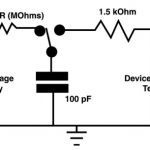

Device Noise Analysis, What Not to Do for AMS IC Designs

AMS IC designers have a lot to think about when crafting transistor-level designs to meet specifications and schedules, so the most-used tool in their kit is the trusted SPICE or FastSPICE circuit simulator to help analyze timing, power, sensitivity and even device noise. I just did a Google search for “device noise analysis… Read More

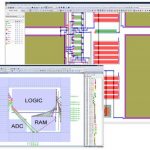

Methodology Help for Analog IC Designers

Digital designers are more numerous than analog IC designers, and so they tend to get more attention from EDA vendors in terms of tools and automation methodologies. For an analog design team with specialists focused separately on schematics and layout there are several methodology questions that need to be addressed, like:… Read More

Benefits of Using Schematic Driven Layout

Most IC designs are developed by a team of professionals, often separated into distinct groups like front-end and back-end, logical and physical designers. Circuit designers use tools like schematic capture at the transistor-level to create a topology, then begin simulating the netlist with a SPICE simulator. Layout designers… Read More

IC Design at ZMDI

As a blogger I have the privilege of meeting many IC designers from around the world, mostly through contact on LinkedIn or from connecting at trade shows. Through a contact at DACI met up with Achim Graupner, a manager of methodology and design automation from ZMDI, then asked him for an interview to understand how his group does … Read More

Transistor-Level IC Design is Alive and Thriving

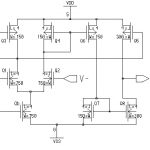

There’s much talk in EDA about High Level Synthesis (HLS), Transaction Level Modeling (TLM) and the Universal Verification Methodology (UVM), however there’s a lower-level of abstraction, the transistor-level, where high-speed digital cell libraries are created, analog circuits are crafted, and AMS designers… Read More

Designing SmartCar ICs

When I upgraded cars from a 1988 to 1998 Acura it seemed like my car had become much smarter with a security chip in the key, security codes in the radio and a connector for computer diagnosis, however in today’s modern auto there’s a lot more mixed-signal design content. Micronasand Synopsysgot together and hosted … Read More

Ensuring ESD Integrity

Electro Static Discharge (ESD) is a fact of life for IC designs and has been ever since electronics were first created and then started failing because of sudden, large currents flowing through the design caused by human, processing or machine contact. It’s just too expensive to layout an IC today, fabricate it, test for … Read More