Our laptops and desktop computers have billions of transistors in their application processor chips, yet I often don’t consider the reliability effects of aging that the transistors experience in the chips. At the recent Synopsys User Group (aka SNUG), there was a technical presentation on this topic from Srinivas Bodapati,… Read More

Tag: hspice

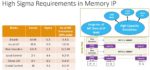

Making Full Memory IP Robust During Design

Looking at a typical SoC design today it’s likely to contain a massive amount of memory IP, like: RAM, ROM, register files. Keeping memory close to the CPU makes sense for the lowest latency and highest performance metrics, but what about process variations affecting the memory operation? At the recent DAC conference held… Read More

Unexpected Help for Simulation from Machine Learning

I attend a lot of events on machine learning and write about it regularly. However, I learned some exciting new information about machine learning in a very surprising place recently. Every year for the last few years I have attended the HSPICE SIG dinner hosted by Synopsys in Santa Clara. This event starts with a vendor fair featuring… Read More

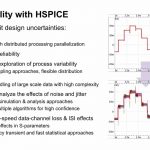

Using HSPICE StatEye to Tackle DDR4 Rail Jitter

The world is a risky place, according to Scott Wedge, Principal R&D Engineer at Synopsys, who presented at the Synopsys HSPICE SIG on Feb 2[SUP]nd[/SUP] in Santa Clara. Indeed, the world circuit designers face can be uncertain. Dealing with risk and departure from ideal was a main theme in the fascinating talks at this dinner… Read More

Circuit Simulation Videos Show How To

One of the things that I miss most about attending trade shows like DAC in the old days was that you actually got to see EDA tools being demonstrated live in the exhibit area. You could see what the GUI looked like, how the dialogs worked, and learn what kind of control you could have during analysis. Most of what you see today at DAC in the… Read More

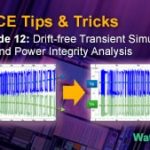

Drift is a Bad Thing for SPICE Circuit Simulators

My first job out of college was with Intel, located in Aloha, Oregon and I did circuit simulations using a proprietary SPICE circuit simulator called ASPEC that was maintained in-house. While doing some circuit simulations one day I noticed that an internal node in one of my circuits was gradually getting higher and higher, even… Read More

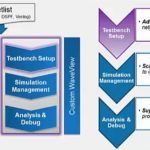

Synopsys’ New Circuit Simulation Environment Improves Productivity — for Free

When technology advances, complexities increase and data size becomes unmanageable. Fresh thinking and a new environment for automation are needed to provide the required increase in productivity. Specifically in case of circuit simulation of advanced-node analog designs, where precision is paramount and a large number… Read More

HSPICE – 35 and looking good!

A maturetool. A legacytool. A tool that’s a little long in the tooth. We have all used these terms to refer to an EDA product that has not been able to keep up with technical challenges of model complexity, performance, or new features required by current SoC and system design requirements.… Read More

FinFET Reliability Analysis with Device Self-Heating

At the recent TSMC OIP symposium, a collaborative presentation by Synopsys and Xilinx highlighted the importance of incorporating the local FinFET device self-heating temperature increase on the acceleration of device reliability mechanisms.… Read More

Circuit Simulation Update from #52DAC

Actual users of circuit simulators told their design and simulation stories at DAC during a luncheon sponsored by Synopsys on June 8th. I always prefer to hear from a design engineer versus a marketing person about what tool they use for circuit simulation, and how it helps them analyze their design goals. This year there were engineers… Read More