At Hot Chips 2025, Philippe Sauter of ETH Zürich presented Basilisk, a project that may redefine what’s possible with open-source hardware. Basilisk is a 34 mm² RISC-V SoC fabricated at IHP Microelectronics on its open-source 130nm BiCMOS process in Germany. Basilisk, named after the Greco-Roman mythical creature known… Read More

Tag: hot chips

eSilicon Brings a New Software Interface to its 7nm neuASIC Machine Learning Platform at Hot Chips

In early May of this year, eSilicon announced the tape-out of a test chip which included the latest additions to its neuASIC™ IP platform. At the upcoming Hot Chips Symposium to be held at Stanford on August 19 and 20, 2019, eSilicon will be demonstrating the software component of this AI-enabling IP platform. At the event, eSilicon… Read More

Neural Network Efficiency with Embedded FPGA’s

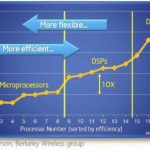

The traditional metrics for evaluating IP are performance, power, and area, commonly abbreviated as PPA. Viewed independently, PPA measures can be difficult to assess. As an example, design constraints that are purely based on performance, without concern for the associated power dissipation and circuit area, are increasingly… Read More

Meet the POWER9 Chip Family

When you looked at a chip in the past you primarily were concerned with two things: the speed of the chip, usually expressed in GHz, and how much power it consumed. Today the IBM engineers preparing the newest POWER chip, the 14nm POWER9, are tweaking the chips for the different workloads it might run, such as cognitive or cloud, and… Read More

The Chip Design Game at the End of Moore’s Law

I just came across and interesting video from last year’s Hot Chips conference. Dr. Robert Colwell of DARPA discusses how the processor design industry is likely to change after it becomes too difficult to continue scaling transistors to ever-smaller dimensions. This is likely to occur sometime within the next decade,… Read More