In the semiconductor industry High-Level Synthesis (HLS) and SystemC have become essential tools, allowing engineers to model complex hardware designs using familiar C/C++ constructs. Yet, despite the widespread adoption of these languages, the debugging workflows in hardware development lag far behind those in software… Read More

Tag: hls

Moving Beyond RTL at #62DAC

Hardware designers have been using RTL and hardware description languages since the 1980s, yet many attempts at moving beyond RTL have tried to gain a foothold. At the #62DAC event I spent some time with Mike Fingeroff, the Chief High-Level Synthesis Technologist to understand what his company Rise Design Automation is up to. … Read More

An Imaginative Approach to AI-based Design

DVCon 2025 was unquestionably a forum for pulling out all the stops in AI-based (RTL) design and verification, particularly around generative AI and agentic methods. I heard three product pitches and a keynote and have been told that every AI talk was standing room only. A pitch from Rise-DA particularly appealed to me because … Read More

Something new in High Level Synthesis and High Level Verification

As SoC complexities continue to expand to billions of transistors, the quest for higher levels of design automation also rises. This has led to the adoption of High-Level Synthesis (HLS), using design languages such as C++ and SystemC, which is more productive than traditional RTL design entry methods. In the RTL approach there… Read More

New Tool that Synthesizes Python to RTL for AI Neural Network Code

AI and ML techniques are popular topics, yet there are considerable challenges to those that want to design and build an AI accelerator for inferencing, as you need a team that understands how to model a neural network in a language like Python, turn that model into RTL, then verify that your RTL matches Python. Researchers from CERN,… Read More

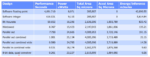

A Fresh Look at HLS Value

I’ve written several articles on High-Level Synthesis (HLS), designing in C, C++ or SystemC, then synthesizing to RTL. There is unquestionable appeal to the concept. A higher level of abstraction enables a function to be described in less lines of code (LOC). Which immediately offers higher productivity and implies less bugs… Read More

HLS in a Stanford Edge ML Accelerator Design

I wrote recently about Siemens EDA’s philosophy on designing quality in from the outset, rather than trying to verify it in. The first step is moving up the level of abstraction for design. They mentioned the advantages of HLS in this respect and I refined that to “for DSP-centric applications”. A Stanford group recently presented… Read More

Smoother MATLAB to HLS Flow

It hard to imagine design of a complex signal processing or computer vision application starting somewhere other than in MATLAB. Prove out the algorithm in MATLAB, then re-model in Simulink, to move closer to hardware. First probably an architectural model, using MATLAB library functions to prove out behavior of the larger system.… Read More

#57DAC – Panel Discussion of High Level Synthesis

Presenters took a trip down memory lane at DAC this year by having a panel discussion on HLS (High Level Synthesis) spanning from 1974 to 2020, and that time period aligns with when I first graduated from the University of Minnesota in 1978, starting chip design at Intel, then later transitioning into EDA companies by 1986. Marilyn… Read More

What a Difference an Architecture Makes: Optimizing AI for IoT

Last week Mentor hosted a virtual event on designing an AI accelerator with HLS, integrating it together with an Arm Corstone SSE-200 platform and characterizing/optimizing for performance and power. Though in some ways a recap of earlier presentations, there were some added insights in this session, particularly in characterizing… Read More