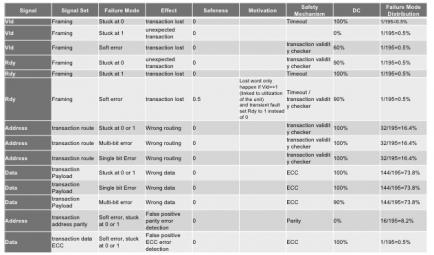

In the course of building my understanding of functional safety, particularly with respect to ISO 26262, I have developed a better understanding of the design methods used to mitigate safety problems and the various tools and techniques that are applied to measure the impact of those diagnostics against ASIL goals. One area in… Read More

Tag: hierarchical

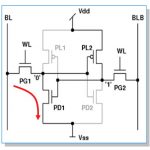

Optimizing SRAM IP for Yield and Reliability

My IC design career started out with DRAM at Intel, and included SRAM embedded in GPUs, so I recall some common questions that face memory IP designers even today, like:

- Does reading a bit flip the stored data?

- Can I write both 0 and 1 into every cell?

- Will read access times be met?

- While lowering the supply voltage does the cell data retain?

A Robust Lint Methodology Ensures Faster Design Closure

With the increase in SoC designs’ sizes and complexities, the verification continuum has grown larger to an extent that the strategies for design convergence need to be applied from the very beginning of the design flow. Often designers are stuck with never ending iterations between RTL, gate and transistor levels at different… Read More

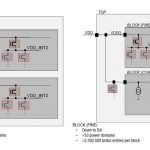

Robust Design <- Robust Flow <- Robust Tools

I could have written the sequence of the title in reverse order, but no, design is the one which initiates the need of a particular flow and the flow needs support of EDA tools to satisfy that need. It’s okay if the design is small; some manual procedures and workarounds/scripts may be able to perform certain jobs. However, as the design… Read More