AI, hyperscale data centers, and data-intensive workloads are driving unprecedented demands for performance, bandwidth, and energy efficiency. As the economic returns of traditional transistor scaling diminish, advanced IC packaging and heterogeneous integration have become the primary levers for system-level scaling.… Read More

Tag: hierarchical design

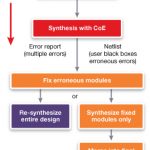

Conquering errors in the hierarchy of FPGA IP

FPGA design today involves not only millions of gates on the target device, but thousands of source files with RTL and constraints, often generated by multiple designers or third party IP providers. With modules organized in some logical way describing the design, designers brace themselves for synthesis and a possible avalanche… Read More

Stick to the script for repeatable FPGA-based prototyping

70% of today’s ASIC and SoC designs are being prototyped on FPGAs. Everybody knows that. But, did you know that automating the process of converting what could be thousands of ASIC “golden” files into FPGA-friendly versions can mean big savings in a large design?… Read More

Second FPGA to the right, and straight on ‘til it works

In a fantasy world where there were no coding errors or integration issues, FPGA designs would fly straight through synthesis easily and quickly. Maybe that world does exist somewhere. For the rest of us, who have experienced the agony of running a large FPGA design – again – only to find another error and have to start over, there … Read More