I wrote earlier about managing service-level risk in SoC design, since the minimum service level a system can guarantee under realistic traffic is critical to OEM guarantees of dependable system performance. An ABS design which might get bogged down in traffic under only 0.1% of scenarios is of no use to anyone. That said, meeting… Read More

Tag: floorplan

NoC-Based SoC Design. A Sondrel Perspective

Why are NoCs important in modern SoCs and what are best design practices for using NoC? As always, a great place to start is the perspective of an SoC design organization which depends on pumping out high performance designs. Sondrel is a turnkey ASIC service provider, covering the spectrum from system design to silicon supply. … Read More

Experimenting for Better Floorplans

There is sometimes an irony in switching to a better solution in design construction or analysis. The new approach is so much better that you want to experiment to further optimize the design. Which then exposes another barrier to enjoying that newfound freedom. SoC design teams often find this when switching from crossbar interconnect… Read More

Decisive Floorplanning for Faster Design Closure

Semiconductor design automation at system level is gaining its due importance today. It needs an effective, efficient, and seamless flow from system up to silicon. There is lot of effort going on for automating SoC design exploration at system level but that eventually stops at RTL; another level of flow automation takes over … Read More

Automating Timing Closure Using Interconnect IP, Physical Information

Timing closure is a “tortoise” for some system-on-chip (SoC) designers just the way many digital guys call RF design a “black art”. Chip designers often tell horror stories of doing up to 20 back-end physical synthesis place & route (SP&R) iterations with each iteration taking a week or more. “Timing closure”, a largely… Read More

Cadence’s New Implementation System Promises Better TAT and PPA

On Tuesday Cadence made a big announcement about their new physical implementation offering, Innovus, during the keynote address at the CDNLive event in Silicon Valley. Cadence CEO Lip-Bu Tan alluded to it during his kick off talk, and next up Anirudh Devgan, Senior Vice President, Digital & Signoff Group, filled in more … Read More

Untangling snags earlier and reducing area by 10%

The over 20 years of experience behind Synopsys Design Compiler is getting a new look for 2014, and we had a few minutes with Priti Vijayvargiya, director of product marketing for RTL synthesis, to explore what’s in the latest version of the synthesis tool.

Previewed today, Synopsys Design Compiler 2013.12 continues to target … Read More

Mentor Buys Oasys

Mentor is acquiring Oasys, subject to all the usual caveats about shareholder and regulatory approval. The shareholder paperwork went out earlier this week. The common stock is valueless so presumably the price is low (and Mentor historically has not paid high prices for its acquisitions).

So what is going to happen with the technology?… Read More

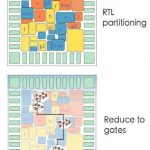

Floorplanning Merged With Synthesis

One area of iteration that is becoming more problematic is between floorplanning and synthesis. So much of timing is driven by placement that fixing timing and even power often involves not just re-synthesis and re-placement but alterations to the floorplan. The Achilles heel of existing methods is that floorplanning tools … Read More

Oasys Announces Floorplan Compiler

Today Oasys announced the availability of Floorplan Compiler in the Oasys RealTime suite of physical RTL exploration and synthesis tools. This is actually a repackaging of a capability that has always been in RealTime Designer, and in fact has been an important aspect of how well RealTime Designer has performed in benchmarks … Read More