In the early years of Cadence their growth was bolstered through many well-timed acquisitions, however over the last several years I’ve noticed a distinctively different trend where they have internally developed EDA tools. I had a Zoom call with Jay Madiraju from Cadence, who markets their newly announced Fast SPICE … Read More

Tag: fast spice

White Paper – Mixed Signal Verification for Nanometer SOCs

The number of touchpoints between analog and digital circuits in high performance SoCs is increasing. This is not a problem because it is possible to implement critical analog blocks directly on nanometer scale digital ICs. However, in many cases digital interfaces or digital feedback circuitry configures these analog blocks… Read More

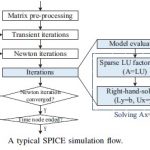

The Emerging Importance of Parallel SPICE

SPICE simulation is the workhorse tool for custom circuit timing validation and electrical analysis. As the complexity of blocks and macros has increased in advanced process nodes — especially with post-layout extraction parasitic elements annotated to the circuit netlist — the model size and simulation throughput… Read More

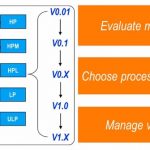

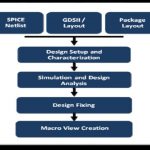

Process Development, CAD and Circuit Design

Working at Intel as a circuit designer I clearly remember how there were three distinct groups: Process Development, CAD and Circuit Design. Each of the groups sat in a different part of the building in Aloha Oregon, we had different job titles, different degrees, spoke with different acronyms and yet we all had to work together … Read More

Xilinx & Apache Team up for FPGA Reliability at 20nm

In this age of SoCs with hundreds of IPs from different sources integrated together and working at high operating frequencies, FPGA designers are hard pressed keeping up the chip reliability from issues arising out of excessive static & dynamic IR drop, power & ground noise, electro migration and so on. While the IPs are… Read More

Device Noise Analysis of Switched-Capacitor Circuits Webinar

Switched-capacitor (SC) circuits are ubiquitous in CMOS mixed-signal ICs. Thermal noise, introduced by MOS switches and active amplifier circuitry, is the major performance limiter in these circuits. This webinar reviews analysis techniques to accurately analyze the noise performance of switched-capacitor circuits … Read More

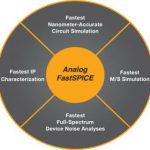

A Brief History of Berkeley Design Automation

Analog, mixed-signal, RF, and custom digital circuitry implemented in GHz nanometer CMOS introduce a new class of design and verification challenges that traditional transistor‑level simulators cannot adequately address. Berkeley Design Automation, Inc., (BDA) was founded in 2003 by Amit Mehrotra and Amit Narayan,… Read More

A Brief History of SPICE

SPICE is an acronym for Simulation Program with Integrated Circuit Emphasis and represents a class of EDA software used by circuit designers at the transistor-level to predict the timing, frequency, voltage, current or power of an IC or interconnect before fabrication.

In 1971 there was a tool called CANCER (Computer Analysis… Read More

Fast Monte Carlo and Analog Fast SPICE

Britto Vincent of ProPlus Design Solutions met with me at DAC on Monday morning to talk about Design For Yield (DFY) and Analog Fast SPICE.

In 2011 ProPlus announced DFY tools where the technology came from IBM, it provides fast Monte Carlo results up to 3 sigma, then added NanoSpice for faster simulation results. Similar in approach… Read More

When analog/RF/mixed-signal IC design meets nanometer CMOS geometries!

In working with TSMC and GlobalFoundries on AMS design reference flows I have experienced first hand the increasing verification challenges of nanometer analog, RF, and mixed-signal circuits. Tools in this area have to be both silicon accurate and blindingly fast! Berkeley Design Automation is one of the key vendors in this … Read More