You are currently viewing SemiWiki as a guest which gives you limited access to the site. To view blog comments and experience other SemiWiki features you must be a registered member. Registration is fast, simple, and absolutely free so please,

join our community today!

One of TSMC’s two big Silicon Valley events each year is the Open Innovation Platform (OIP) Forum. This year it is on Tuesday October 1st. It is in the San Jose Convention Center and starts at 9am (registration opens at 8am). Pre-registration to attend is now open here or click on the image to the right.

From 9.10 to 9.40 is the … Read More

The existence of TSMC’s Open Innovation Platform (OIP) program further sped up disaggregation of the semiconductor supply chain. Partly, this was enabled by the existence of a healthy EDA industry and an increasingly healthy IP industry. As chip designs had grown more complex and entered the system-on-chip (SoC) era, the amount… Read More

It is beginning to look as if 28nm transistors, which are the cheapest per million gates compared to any earlier process such as 45nm, may also be the cheapest per million gates compared to any later process such as 20nm.

What we know so far: FinFET seems to be difficult technology because of the 3D structure and so the novel manufacturing… Read More

Today TSMC announced three reference flows that they have been working on along with various EDA vendors (and ARM and perhaps other IP suppliers). The three new flows are:

- 16FinFET Digital Reference Flow. Obviously this has full support for non-planar FinFET transistors including extraction, quantized pitch placement, low-vdd

…

Read More

At TSMC’s OIP on October 1st, Mentor Graphics have 5 different presentations. Collect the whole set!

11am, EDA track. Design Reliability with Calibre Smartfill and PERC. Muni Mohan of Broadcom and Jeff Wilson of Mentor. New methodologies were invented for 28nm for smart fill meeting DFM requirements (and at 20nm me may … Read More

The history of TSMC and its Open Innovation Platform (OIP) is, like almost everything in semiconductors, driven by the economics of semiconductor manufacturing. Of course ICs started 50 years ago at Fairchild (very close to where Google is headquartered today, these things go in circles). The planarization approach, whereby… Read More

If you have been to an Ajit Manocha keynote recently, he talks a lot about Foundry 2.0. I covered his keynote at Semicon West in July here. Dan Hutcheson of VLSI Research interviewed Ajit about this new business model to identify it, see how it was different and see how GlobalFoundries were executing the model differently from the … Read More

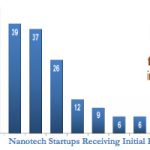

At the recent GSA Entrepreneurship Forumone of the panelists was Angel Orrantia of Innopartners who are trying a novel approach to funding startups in the semiconductor space and the surrounding ecosystem.

It seems things got started with an innovation center inside SK Hynix. Just in case you have forgotten, Hynix is the newish… Read More

TSMC announced their Q2 financial results yesterday. Revenue was $5.2B (at the high end of guidance) with net income of $1.6B. This is up 17.4% on Q1 and up 21.6% year-to-year. Gross margin is up too, at 49% which is up 3.2 points on Q1 and 0.3 points year-to-year. As usual the financial results are not directly that interesting since… Read More

Novati is a semiconductor company that you probably haven’t heard of. It has its roots in Sematech back when Sematech was mainly in Austin rather than New York where it is today. The Sematech fab first became an independent company and then acquired by SVTC and operated under that name for 4 years. Finally, last the investors… Read More